DMG-CPU Cells Reference

This document provides information about the cells found in the Gameboy DMG-CPU-B die shots. It builds on the work of Furrtek, the information found in his DMG-CPU-Inside repository.

I was in the process of tracing back all the connections from the CPU and was constantly encountering cells for which the cell zoo JPG wasn't providing the pinout, so I wanted to have them all documented once and for all, to make life easier!

Compared to Furrtek's schematics, some cells have been renamed, because they didn't fit the naming scheme of having all cells within the same column or row starting with the same letter. Some I/O pads were also renamed, because the names did not fit the official documents.

Special thanks to ogamespec. He made some very detailed poly/active layer pictures for me.

You can find a cleaned up version of the Game Boy chip schematics for KiCad and the overlay SVG file here.

Please report any errors I made here.

- Basic logic gates

- Compound logic gates

- Arithmetic gates

- Tri-state drivers

- Storage elements

- NAND_LATCH

- NOR_LATCH

- DLATCH_EE (A)

- DLATCH_EE_Q (A2)

- DLATCH (B)

- DRLATCH_EE

- DFFR_CC_Q (A)

- DFFR_CC (B)

- DFFR (B2)

- DFFSR

- TFFNL

- I/O pads

- PAD_BIDIR (A)

- PAD_BIDIR_PU (B)

- PAD_BIDIR_PU_LATCH (C)

- PAD_IN (A)

- PAD_IN_PU (B)

- PAD_OUT (A)

- PAD_OUT_DIFF (B)

- PAD_XTAL

- PAD_PASS

- PAD_PASS_TG

- Analog

- Other

Basic logic gates

NOT gates

NOT_X1 (A)

Simple inverter.

|

|

Instances: ABAF ABEZ ABOL ABUP ABUR ACOR ADAH ADAR ADOK AFAT AFEC AFEP AGET AGUR AHOF AJAX AKAF AKOL AKUG ALES ALOP ALYP AMUN AMYG APAM APAT APUV AROP AROV ARUC ARYF ARYS ASAD ASYP ASYS ATAG ATAR ATEC ATEZ ATUP ATUS ATYP ATYV AVUN AWOH AXAD AXYN AZEG AZOR AZYB BACA BADY BAFU BAGY BAJA BAKO BALU BALY BAMA BANE BARU BASE BASU BATA BAVU BAWA BAZE BEBA BEDE BEFA BEJE BEKA BELA BELE BELO BEPE BERO BETE BODE BODO BOFE BOFU BOFY BOGE BOJO BOKA BOKY BONE BOPO BOXY BUCO BUCY BUDA BUDU BUFE BUFO BUGO BUGY BUKA BUKO BUTY BUWA BUWE BUWY BUXO BUXU BUZE BUZY BYFU BYGO BYHO BYJO BYKO BYLO BYMA BYMO BYMY BYRU BYSU BYVA BYVY BYXO BYZO CABE CACA CACU CAGE CALA CALU CAMU CAMY CANU CAPE CARA CATE CATY CAVO CAXU CEGE CEGU CELE CELO CEPO CEPY CETO CEXE CEXU COBA CODO COFU COGO COGU COJU COKE CONA CONE COPE COSA COSE COZY CUGO CULE CURE CURU CUSO CUTO CUWA CYBE CYBO CYGU CYKY CYLA CYLU CYMU CYPY CYTE CYWU DABU DABY DAFO DAJO DAKO DAKU DAPU DAPY DARE DASA DAVU DEBO DECU DECY DEFU DEGA DEGE DEHO DEKE DERO DERU DOCA DOKU DOPU DORU DOSY DOTU DOVO DUBO DUGE DUKA DUKE DULA DULO DUVO DYBA DYHU DYKE DYLU DYMO DYNA DYRO EBOS EDEL EDEN EDEP EJAD EKUD ELYG EMUT ENOB EPEK ERED EROG ERUM ETUK ETUV EWOT EZAS FABO FAJA FAJU FAKA FALU FAZO FEBY FEFO FEKA FEMO FEPU FERY FEVO FEXO FOFA FOGE FOHY FOKU FONE FUFO FUKE FUKY FULE FUME FURU FUVE FUXU FYCU FYRE FYRY FYXO GABA GACE GADE GADO GAFY GAGO GAJA GAJY GALA GALU GAMY GASE GASO GAXO GAZE GECY GEFE GEKA GEKE GEKU GENO GENU GENY GEPA GEPU GESE GETO GEWY GEXE GEXY GOMA GONY GORY GOTE GOVE GUCY GUFA GUFO GUGO GULO GULU GUNU GUPO GURE GURO GUSA GUSU GUVU GUZU GYBA GYDA GYFO GYPA GYSA GYVE GYVO HAKE HAPU HATO HAXE HEKY HELU HEMA HOTA HOXA HOXE HUCE HUDE HUFA HUNY HYFO HYNE JAGO JAKE JECO JEDE JERA JEVA JOLA JONE JOTU JUJU JULO JUTA JUTY JUWA JYBU JYJA KADO KAGE KAME KANU KAPE KARA KASA KASO KATY KAZO KEBO KEDO KEDY KEKE KENE KERE KESE KOKU KONY KOPA KOPU KOPY KOVA KOVO KUBY KUHA KURA KURY KUXU KYDU KYGY KYHO KYKO KYLO KYPE KYPU KYRU KYSA LADY LAFY LAHE LALA LAMO LAPA LAPE LASE LASY LAVA LAXE LEBU LEHO LEJA LEKE LESA LESO LESY LETY LEVO LEXY LOBY LOFU LOGO LOMA LOME LOMY LORU LOTA LOTE LOXA LOZA LOZO LUBO LUFA LUFE LUHE LUKU LULA LUMA LUMO LURA LUSU LYFE LYHA LYKU LYLE LYRY LYWE MABY MADY MASA MATE MAVU MEHE MEKE MEPA METE MEWY MEXA MEXO MOXE MUGY MUJY MULE MULO MUME MUVE MYFA MYFU MYMA MYRE MYSA MYVO NAKO NALE NARO NELE NENA NENY NEZE NOBO NOCU NOFU NOLO NOLY NUCA NUFA NUKO NUPO NYBE NYFO NYGO PAHA PALY PARU PEBY PEVO POFY POHU POLA PUCO PUSY PYRY PYSU RABO RACO RALO RAPU RATA RATU RAVE RAWA RAZA REDU REHO RENA RERY REVO REVY ROBY ROCO ROGE ROME ROMO RONA ROPY RORO ROSY ROTU ROVE ROXO RUCO RUKY RUMA RUNA RUNO RUVY RUZY RYBA RYCA RYCU RYFE RYGA RYJE RYJU RYLE RYSO RYVE RYZY SAME SANA SAPY SAZA SEBY SEFY SELU SERA SERY SOBA SOCA SOCY SOGY SOHA SOJA SOKA SOLO SONO SORE SOWO SUDO SUGY SULU SURA SYBO SYCY SYLO SYNY SYPY SYRO SYSA SYZO TAFU TAFY TAJO TAVA TAVE TAVY TEFY TEHE TENU TEPA TEPO TEPY TERA TOCA TOCU TOFU TOLA TOLU TOMU TONA TOSA TOTU TOVA TOVO TOVY TUBE TUDA TUJU TUKU TUNE TUVA TYCE TYCO TYTA TYTU UBET UBOT UCOB UDOR UMEK UMER UMOB UREK USEC UTOK UVAR UVYN UVYR VAGE VARO VATE VAVE VEFU VEPE VOBY VODE VOMY VOVA VOXU VUMU VUTY VYCO VYCU VYWA WABE WADO WADU WAFO WALO WAMY WANE WASE WATA WAZY WEBO WEFU WEKA WEKU WELE WEME WENY WEPO WERY WESA WOFO WOKU WOLA WOLO WUFA WUKY WUNA WUNU WUPA WURA WURY WUSE WUZO WYCE WYCO WYLU WYRU XABA XACO XADO XAGA XAHO XAHY XANO XARE XATU XEBE XEFY XEGA XELO XEMU XENA XENO XENU XEPO XERA XOGA XOLA XOTA XOVU XOWO XOZY XUBO XUCA XUCE XUHA XUHO XUHY XUJA XUJY XURA XUSY XYFY XYHA XYKE XYNY XYSO XYVA YAZA YFAG YFOC YFOT YMEV YPUR YRYV YVAL YVOK YVOM YWOK YZET ZABU ZAGE ZAGO ZAPA ZAPE ZEFU ZERA ZERY ZETE ZOCY ZOKE ZUFY ZURU ZUVY ZYBA ZYFO ZYRA ZYRO (747 total) (many inverters for clock complements are missing in this list)

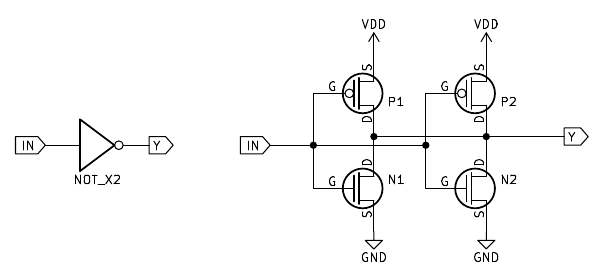

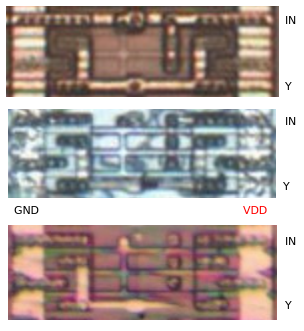

NOT_X2 (B)

Inverter with 2× drive strength.

|

|

Instances: ABEF ABON ABUB ACAM ACOL ADAK ADAZ ADYR AFOB AFOP AHAL AHOC AJAS ALET ALUR AMEL APAR APUX ASAH ASOP ATAF ATAL ATEJ AVAP AZAR AZUB AZUL BAFY BANU BAXY BERU BONO BORU BORY BOWE BUBU BURE BUTU BYFA BYRY CEDE CEHA COKA COTA CUNU CYKE DAPA DAWE DENO DENY DOSO DUCE DUGA DUPA DYDO DYFA DYKY DYLA DYTE DYTY EFUG ELAS EPYT ESUR EVAJ FADO FAME FUPA FURO FUTY GOGE GOWO GUGY GUMU GYGY GYMA HAPO HOVA HOVO KAGY KULY KYNY LABU LACA LALO LEFA LEKO LENA LEXE LOLY LOZE LOZU LUBY LUVE LUVO LUXA MOPA MOSU NUVA PEDU POGU PONY PORE RADA RADY RAGU RARE RAVO RAZO REFO REGE REKU REMY REVU RODU ROFA RONU ROSU RUBE RULY RUMU RURA RYKY RYRO RYTY RYZE SARO SELA SOKY SOLE SUZU SYSY TAGO TEGO TEXY TUJY UVYT VARY VOCA VUMY VYGA WALU WERA WERO WESY WEWU WUDA WUKO WUME WUTA WUTY XAPO XARO XAVY XAYO XAYU XEDA XEDU XOCE XOGY XORE XUPA XUPY XUQU XYME ZAXY ZODO ZOFE ZONE (169 total)

NOT_X3 (C)

Inverter with 3× drive strength.

|

|

Instances: ABUZ ALER AMYT APEF APOV ARYL ATOK BECY BUFY BYFE CAZU CULO EGOR EJYB FYNE HORU KEPY KOFO KYMO MECO MURE PURE RAHU RUZE RYPO TAPU TEDO VOTY VYPU (29 total)

NOT_X4 (D)

Inverter with 4× drive strength.

|

|

Instances: ADAD ASOT BEKO BOLO BUDE BUFA CUPA DOVA HAMA SEGU TALU ZEME (12 total)

NOT_X6 (E)

Inverter with 6× drive strength.

|

|

Instances: AGUZ AMUK AZOF BAVY BEDO BEVA BOGA BOGY BOKE BOMA BOWA BUKE BUKU BYDA BYLY EDEK KEBA (17 total)

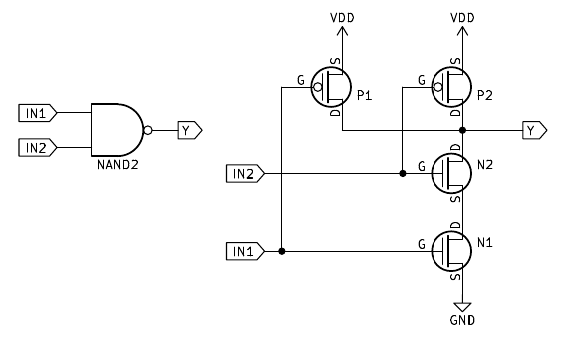

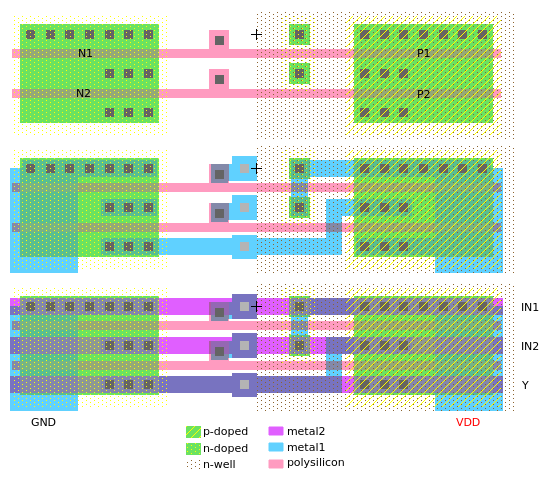

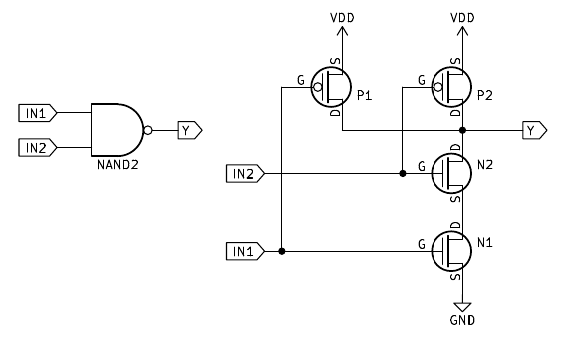

NAND gates

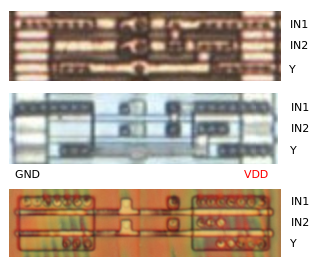

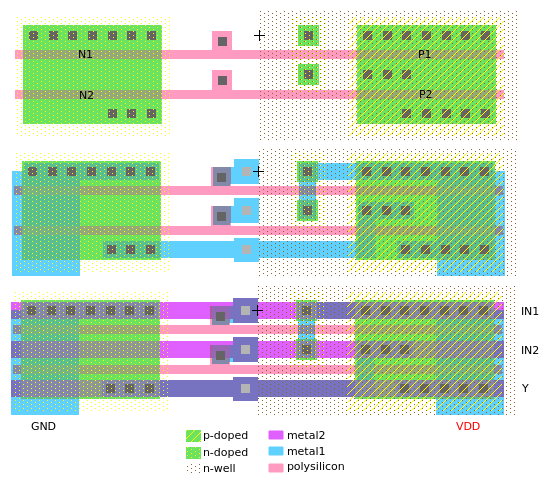

NAND2

NAND gate with two inputs.

|

|

Instances: AFEG AGYN AJEP ANOS AREV AVER AVET BADU BAGE BAGU BALE BARE BEGE BEJU BENA BESO BEXU BOKU BOPY BORO BOSU BOTY BUDO BUGU BUPO BYLA CABA CAZE CEPU CORO CUFU DACE DAXA DEFY DELA DEPU DERY DETA DOCU DOGE DOLA DOLE DULU DURU DYGE EDEL EFEF EGAD EKEM ELER ELOK EPYX ETOL EVYF FAPE FASY FEWA FOVO FOXE GAWA GETA GOLO GOPE GOVO GYLU HAWU HAWY HENU HOLA HOSO HOZU HUMA JORA JURE KAMU KEXU KOLA KOLE KORE KORY KOVU KUPO KYHU KYPA KYRY KYTO LABE LAFU LAKY LAMY LEBO LEKA LELA LEPY LERU LODO LOKO LOKY LOTO LOTY LOWA LUCE LUFY LUJA LUKE LUNU LUTU LYDE LYDU LYRA MADA MAJO MAME MENE MEZU MOFY MORY MOSY MUHO MUNE MYNU MYNY MYTO MYVY MYXA NADY NAJA NEXA NOGU NUTE NYHA NYXO PABE PAMO PAZO PECU PUHE PUME PYZU PYZY RABY RAFY RAGA RAJA RAJO RANO RAPE RAVU REHU RERA ROPE RORA RORY ROXU RUCA RUCE RUDU RUJA RUSY RUTO RUXA RYJA RYJY RYLU RYVO SABE SEBO SEJA SENO SEPY SOHY SOLY SORO SUCA SUCO SUKY SUPU SURE SUZE SYWE TABY TACU TAFA TAME TAPO TEDE TEGU TENA TESO TOWA TUFO TULA TUPE TUWU TUXA TUXE TUXY TYGA TYKO TYRA TYVY UGAC UVER VABY VEXU VUME VUNE WAXO WEDE WEDY WEVO WOKA WUBU WUJA XALA XATO XELY XEXU XODO XOLE XUCY XUKU XYRU XYVE ZADO (225 total)

ECO_NAND2

ECO configurable NAND gate with two inputs.

This variant of the NAND2 gate is only used for some spare cells. It can be converted to a NOR2 gate via metal 1 changes. The layout includes pre-routed vias to facilitate this change during post-silicon ECO.

|

|

Instances: YBYW YCAW YDOS YFAL YHES YJAG YKOR YKUS YKYT YLOH YMEB YNUJ YNYV YTOB YTOR YXAJ YXOW (17 total)

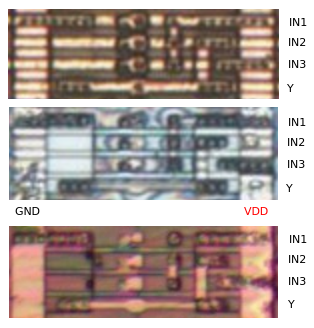

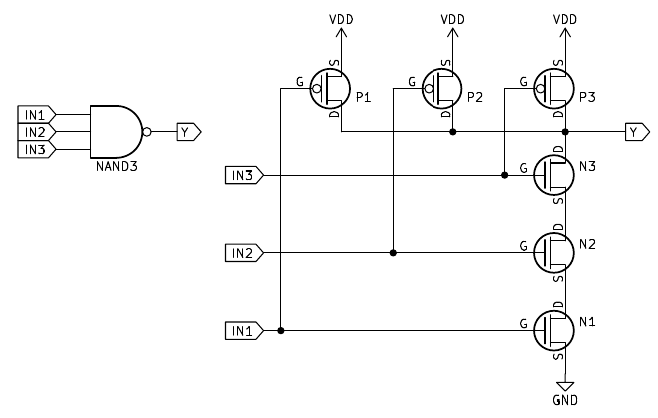

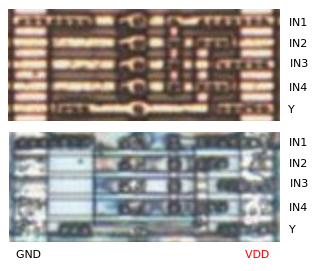

NAND3

NAND gate with three inputs.

|

|

Instances: BOTA BUGE BUTO BYCU DEGO DYDU DYKA EFYL EGOM LARA LAVO MEXU MOCE MODY MYZU NYDY PYHU ROZE TOGA TOME TYNO UPOJ WOLY WUTU XAGE XOFO YBEZ YDUG YGEM YLOZ (30 total)

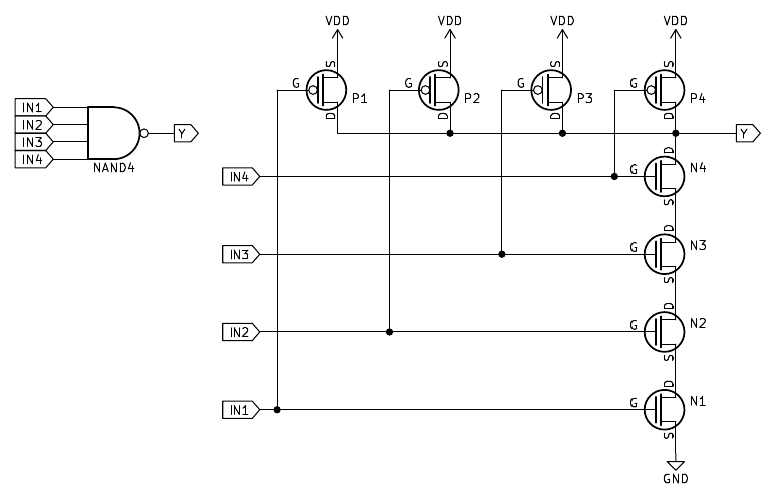

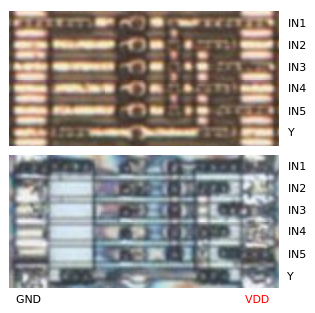

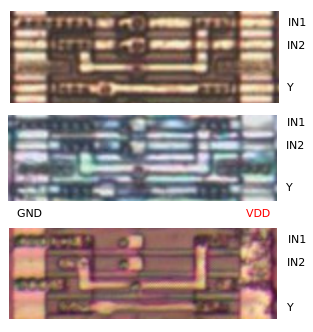

NAND4

NAND gate with four inputs.

|

|

Instances: ACOM ATOZ BEJA CUGU CUPE CUVA DAFY DAMY DATU DAZA DEJY DEWA DEWY DEZO DOGU DONA DUFE DUNO DUPO DURA DUVU EGEN EMAX EMOS ESOT ETUF EXAT FOCO GANY GEBU GUNA REFA ROLO RONE SARA SUVU TEGY TOPE TUGE TYJU URYS UWAM WOMU (43 total)

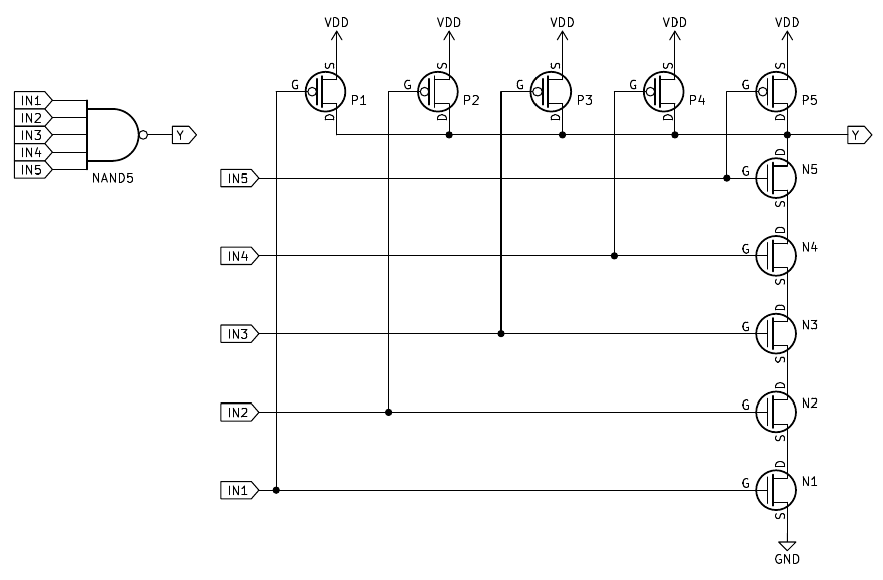

NAND5

NAND gate with five inputs.

|

|

Instances: APER CUTY ERAT FEFY FOVE HUFU NOGY PAFU PALO PUKY VAMA WAGE WATE WAVU WEBU WETA WETY WOFA WORU WYBO WYLE WYVO XUGU (23 total)

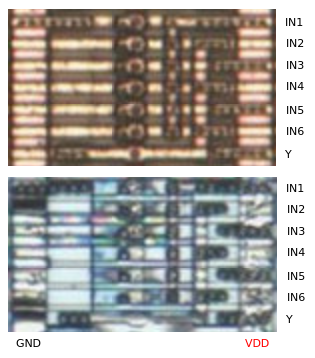

NAND6

NAND gate with six inputs.

|

|

Instances: NAVO WOTA (2 total)

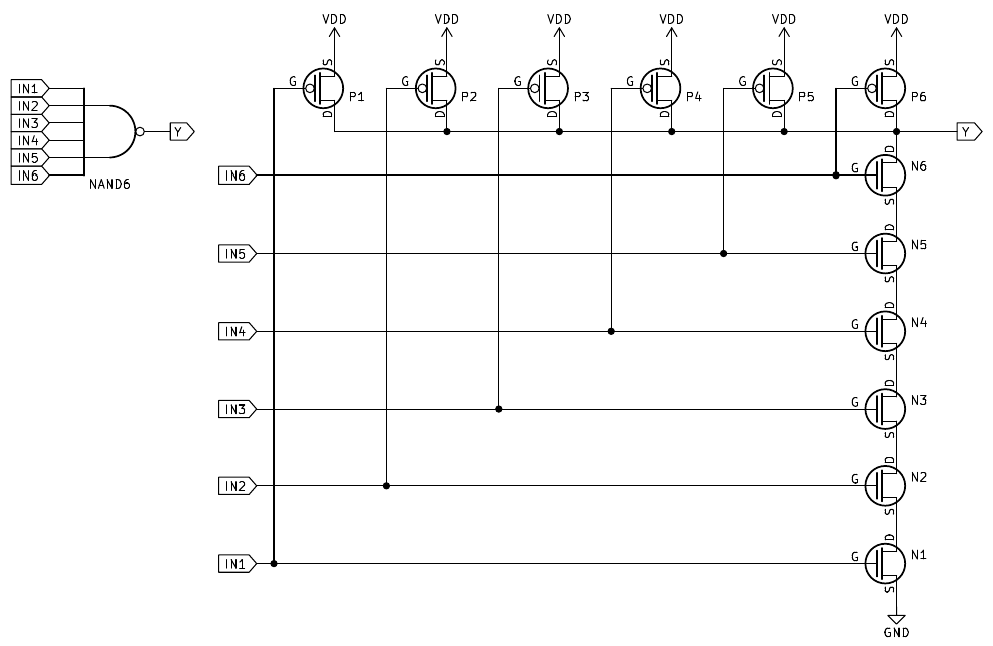

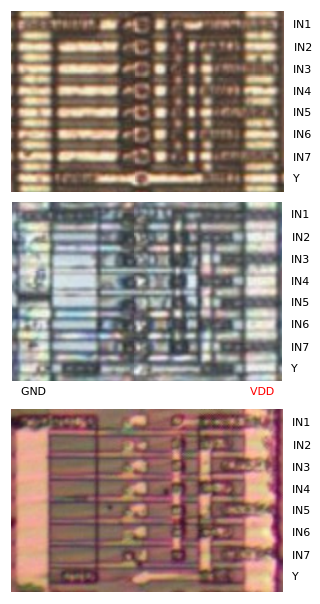

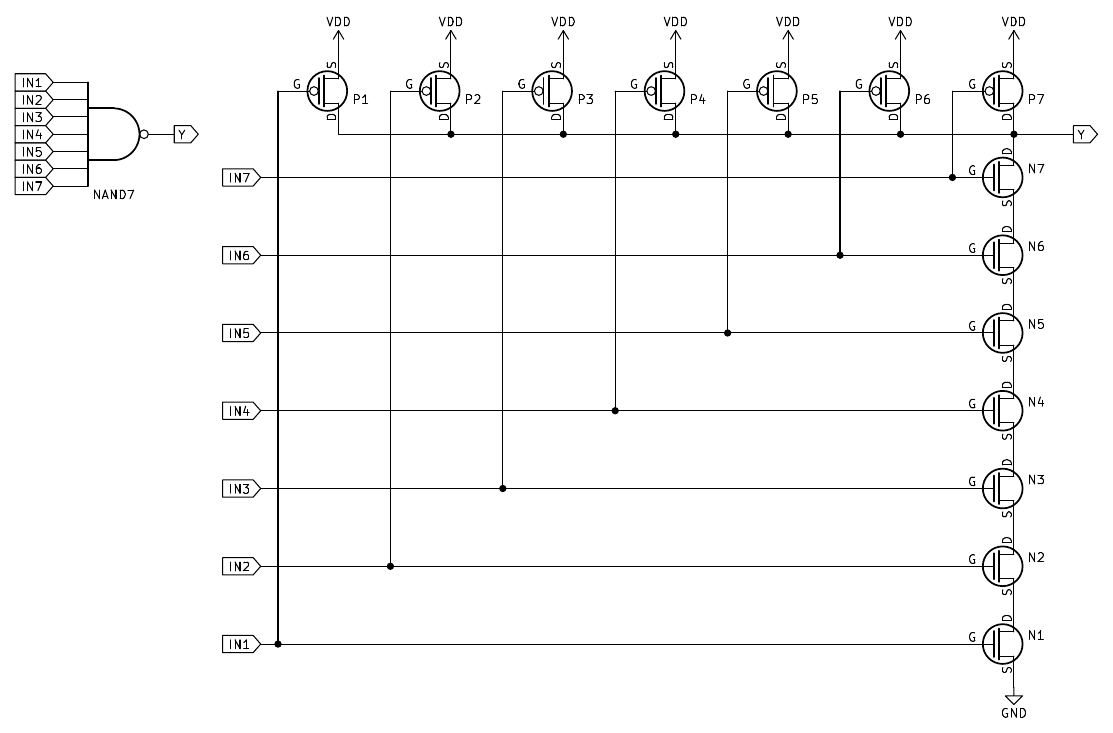

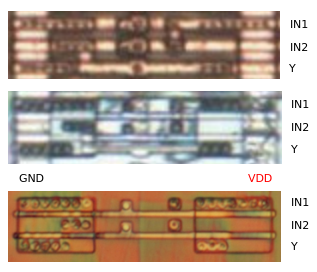

NAND7

NAND gate with seven inputs.

|

|

Instances: TEBO TECE TOZU TUNA VOKU WALE (6 total)

NOR gates

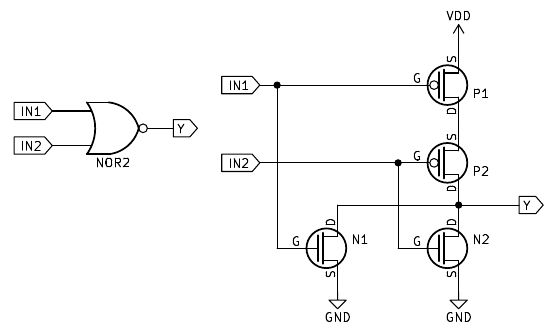

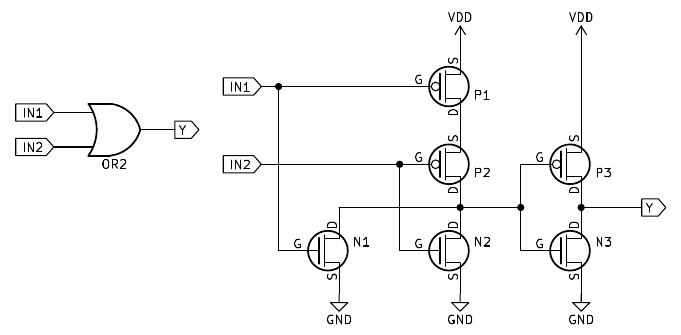

NOR2

NOR gate with two inputs.

|

|

Instances: AFAR AFAS AFUX AGOR AJAV ANOM APAJ APYS ARES ATAT ATYN AVUF AWOD BARO BEFU BELU BEVO BEWO BOLA BOVU BOXO BOXU BUNO BURY BYLE CAFY CAMA CAVA CAXE CAXO CEVU COLO CORA COSO COTU COVO COVY CUGE CYKA DACU DADO DAFA DANU DARA DECO DERA DODY DOJU DOMO DOVE DOXA DOZA DUGO DUJA DUJU DUSA DUTU DYPU DYTA DYVA EDAF EFOR EGET EGYP ELUF EMET EMOL EMOR ENEC ENOK ENUT EPUK EPYK ESEL ETAN EVOL EZUK FAKO FALE FEMY FENY FOXA FULO FURY FUVO GAMO GATO GEFO GEGA GEGE GEMY GOFU GOKA GONO GUNY GUTE GUTU GUVA GUZA GUZE GUZY GYFU GYFY HEFA HEFO HERA HERY HOBU HOLY HURY HYLY HYPA HYVU JADO KABU KAJU KALA KALE KAPO KASY KAZA KETO KORU KOTY KUJO KUKU KYBO KYBU KYWE LAMA LECO LEVA LOSO LUPA LYNY MEGO MENY MERY MOCA MUDE NADA NAFY NAXY NERO NULY PAGU PAHY PANY PASO POME PUKU PUXY PYMA REPA RESY ROGY ROLU RORE RUGY RULO RUNE RYDA RYPU SADU SAKY SEKO SEZE SOBY SOGU SULY SYKE TADY TAMU TEFA TUSO TYMU URUN USUF VEKU VUZA WOJO XANE XATY XOJA (184 total)

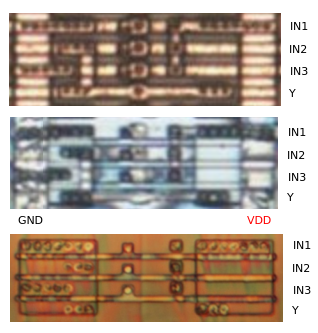

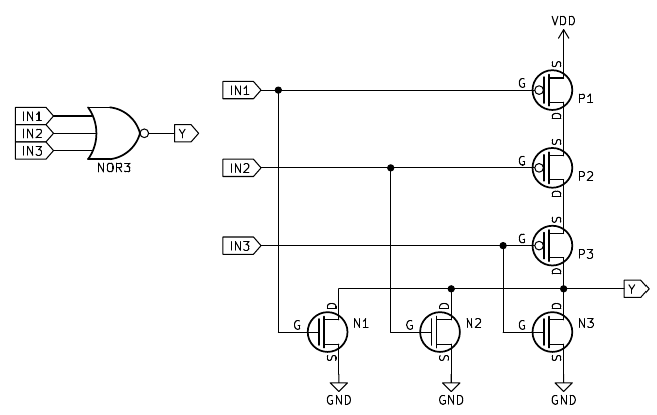

NOR3

NOR gate with three inputs.

|

|

Instances: AJUJ BAPY BATE BENY CAPY CORY DEME DODA DUDU DYRU ELAR EMOF ETAR ETAT ETOV EVER FOWA FURA GAFU GAPY GEPY GUDA GYRE GYRY JUPU KOMA MUDA MYSO NYXU POKA RYDY SECA SYCU TUVO UFOL VYBO XALY (37 total)

NOR4

NOR gate with four inputs.

|

|

Instances: CEHU COGY CYCO CYVY DAJE DAMA EKES EWAM FEHA FYMA GOPA HAFE KORO SEMY SOVU SUBO SUTU XEBA YDOT YKOK YLEV YNAZ YTUB YWAP YWOS ZADU ZAKO ZORO ZURE (29 total)

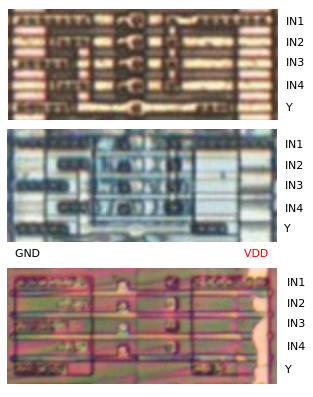

NOR5

NOR gate with five inputs.

|

|

Instances: DARO EMYR FUTE GEVY HANO HOCA SARE (7 total)

NOR6

NOR gate with six inputs.

|

|

Instances: AMUS TYRO (2 total)

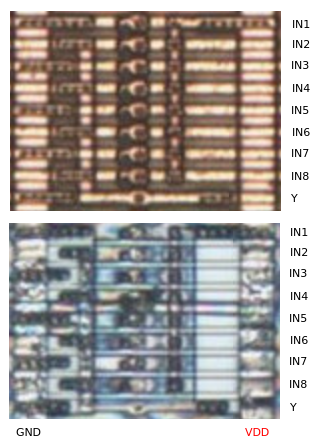

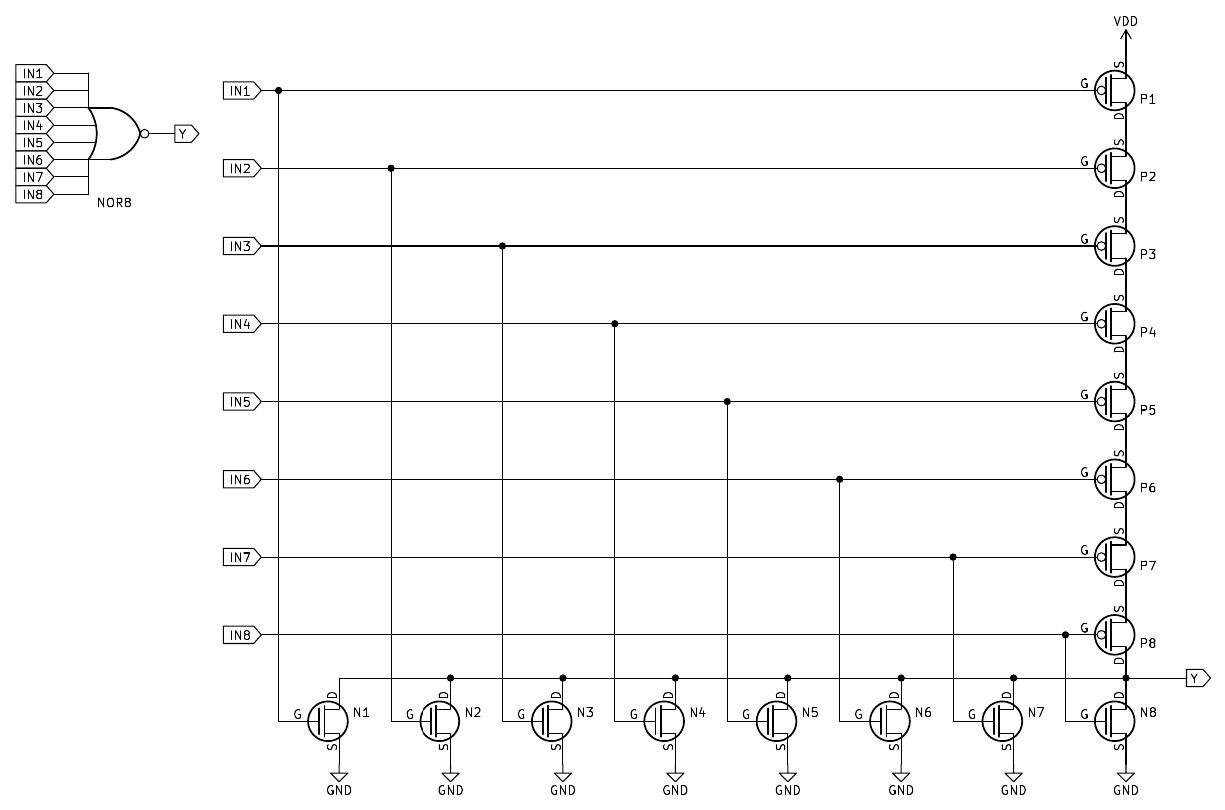

NOR8

NOR gate with eight inputs.

|

|

Instances: NERU TULO (2 total)

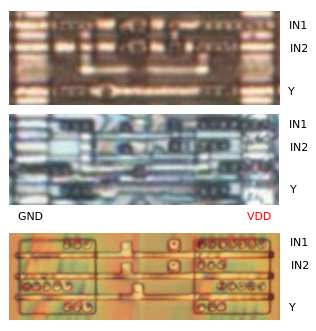

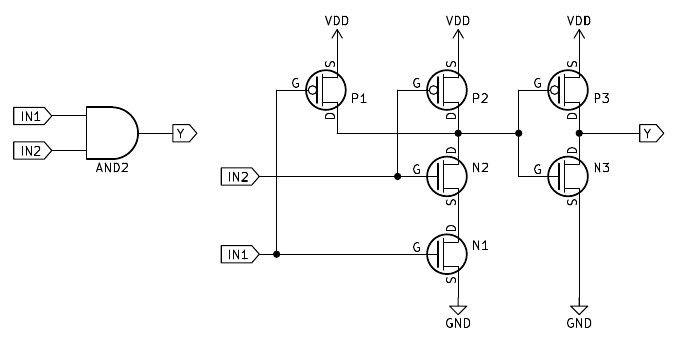

AND gates

AND2

AND gate with two inputs.

|

|

Instances: ABOV ACEG ACEN ACYL AFUG AFYR AGOF AJON AJUX AKOF AMAB AMAC AMOP AMOV ANAN ANAP ANUJ ANYP ANYV APYR AROR ARUR ASOG ASOK ASON ASUL ATUV AVOG AZEM BACU BAKY BAPU BARY BASO BEDY BELY BOJE BOPA BOZA BUVO BUVU BUZA BYKA BYZA BYZY CABY CARO CARY CENU COMO COTE COVU COWE CYFA CYSE DACO DEBY DOKA DORA DORE DOSA DOXY DYMU DYRY EFOP EFOT EGOG EJYF EKEZ EMAR ENEK ENUF EREG ETOK ETUC EVOF EXUC EZOZ FEGA FOKE FOPU FOTO FUJY GAME GAXU GEDO GEJO GERE GETU GOKO HAFU HAGA HUDA HUMO HUPA JAFA JEHY JENU JOCY KAVO KAXY KEVY KOKO KOTA KYFU LAVY LURY META MOFU MOLU MUMY MYXE NETA NUNY POTU POVA POWU RACA RAJY ROCY RUTA RYCE RYFU SAMO SAZO SAZU SEFA SEFU SEMA SEPA SERE SOGO SOHO SOSE SUKE SUMO SUNA SURY TADE TAPA TARU TAXY TEXO TOBA TOBE TODE TOPU TUCA TUFA TUJA TUTO TUTU TYBA UMUT UNOR UNUT VAPE VELY VETU VUSO VYRE WAFA WAFU WARU WAXU WAZU WEFY WEKO WEXE WODU WOXA WUZA WYXY WYZE XAJO XEZE XOMA XONO XUFA XUFY XUKE XULA XUTO XYLE XYLY XYVO YLYC YNYC ZAJE ZAPY ZOLE ZOVY ZUBU ZUFA ZUKO ZYGA ZYKY (197 total)

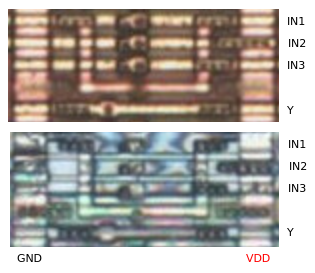

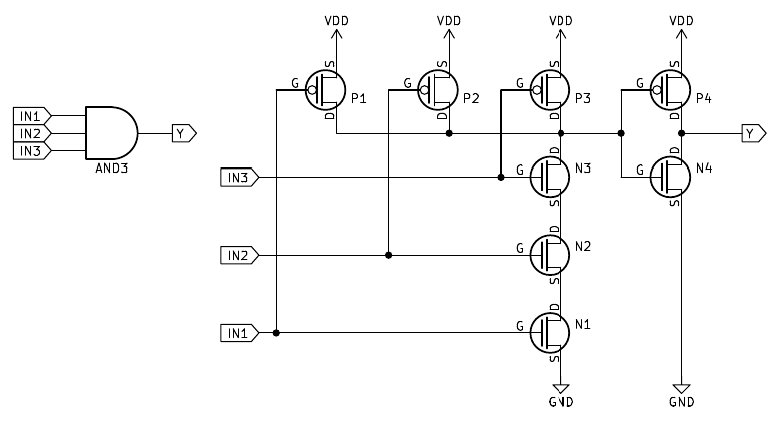

AND3

AND gate with three inputs.

|

|

Instances: ASYT BAVE BUSO CARE COZE CYLU EJEX GUKO HONY HYNO KOTE KYVO LARU LEDO LOPU LYKY LYTA MOVU NUMA NUXO NYPO POBU PYGA RYFO SANO TOZA TUMA TUNY TYFA TYME VATA VOLO VUGO VYRO WUKU YULA (36 total)

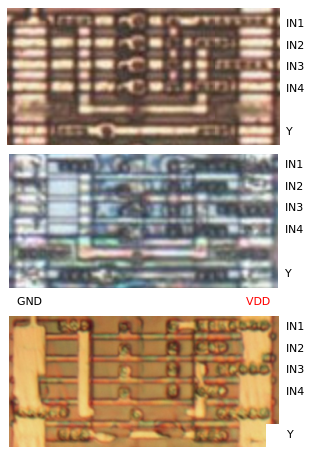

AND4

AND gate with four inputs.

|

|

Instances: ACAT DOFA EKAG FETO NOKO RACU SANU SAPA SORA TACE TAGY TAPE TEDA TEKY TEXE TUBY UCOM UFEG (18 total)

OR gates

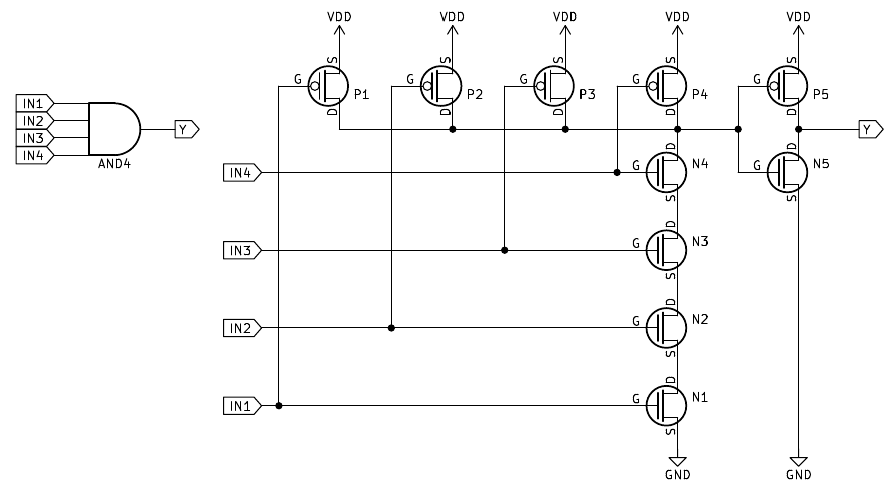

OR2

OR gate with two inputs.

|

|

Instances: ABAK APET ASEN ATYS AVOR BEZY BONU BOTO BOXE BYBY BYJU CADO CAHO CAKE CATO CECU CELA CEMY DATO DAWA DUBU DUPY DYWE EFEV ENUR ERYF EVUR FAVO FEPO FEVE FOKO FUMA FUVA GAKE GAPE GAVA GEDE GEPO GEXA GEZE GORO GOVU GUFY GUKY GURU GUVE GYGA HAMY HASU HEZE HOCU HYLE HYPO JADE JYRO KABA KARU KEKA KEKO KYKU MOTY MUXE MUZU NABE NEVY PAGO PUVA RAKE RELA REPU ROKO RUTE RYNO SACU SAKO SATO SAWU SEDO SEJY SEME SEMU SEWO SOFY SULO SYBU SYMA SYNU TYSO UPYF VUSA WACY WEGO WEJA WOHU WUTO WYLA WYXO XUJO XYLA (99 total)

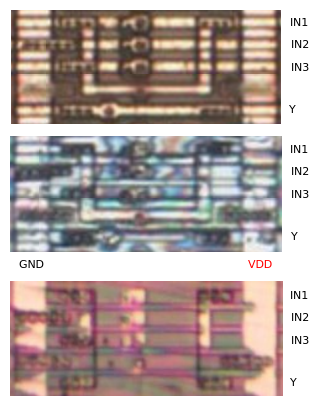

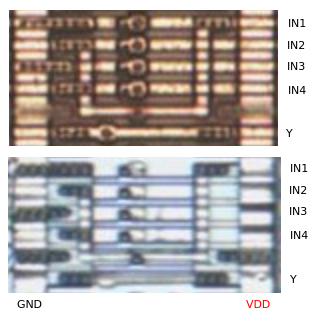

OR3

OR gate with three inputs.

|

|

Instances: ASAM BEBU BETA ESYK FEGY FELO FYGO HOFO KAKE MEFU MEVE MYZO PATY PERO RUDA RUJU TABA TEVO TEVY TORY VOTO VYSA WOPE (23 total)

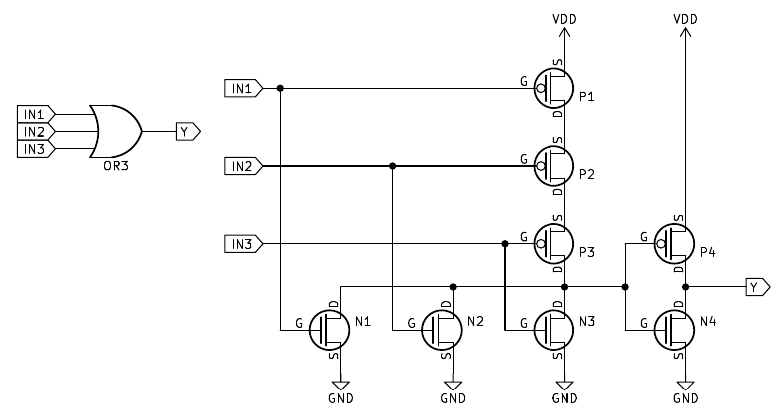

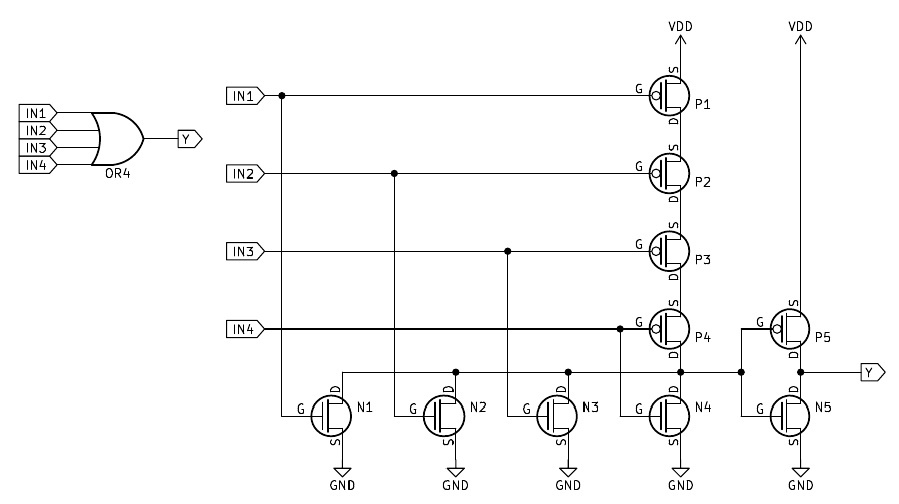

OR4

OR gate with four inputs.

|

|

Instances: ATEG AWET BERY KERY (4 total)

XNOR

XNOR gate with two inputs.

|

|

Instances: HURA MYLO NAZE NEVU NEZO NOJO NONO NORY NUPA NYTU PAGA PASE PEBO PEZO POMO PUHO PUWU SOZU SUHA SYBY (20 total)

XOR

XOR gate with two inputs.

|

|

Instances: BAHU BAZY BOBA BORE BUMY BUVY CALE CEKO CEVA COLA COLU CONY CULU CYLE CYVU DAGA DAGU DAWU DESO DETY DOZO DOZY DUCU DUSE DUZE DYME DYZE EBEF EDYM EJAW EJOT EMYB ESAJ EWOK EWUD FESO FOKY FURE FUZU FYVA GABU GAFE GASU GELA GEVE GOHO GOLA GOLY GOPO GUDE GUZO GYLO HEFY KEFE MAGU RASY REDA ROKU RYBO RYME SAKE SYFU TERY TUCY TYDE TYGE TYKU WAGO WOJU WYZA XAHA XAVU XEGY XEJU XENY XEVA XORA XOSU XUCO YBOX YCAH YDAJ YFOP YFUN YHOK YMAM YPUK YTYP YVAC YVAP YVUZ ZAHA ZAKU ZARE ZATE ZEBA ZEDA ZEFE ZEJO ZEMU ZOGY ZOKY ZULO ZUVU ZUZA ZUZY ZYGO ZYKU ZYPU ZYWU (110 total)

Compound logic gates

AO21

2-1 AND-OR two-level compound gate.

Name in DMG-CPU-Inside: AO3

|

|

Instances: LAGU LOXO TYNU WYJA (4 total)

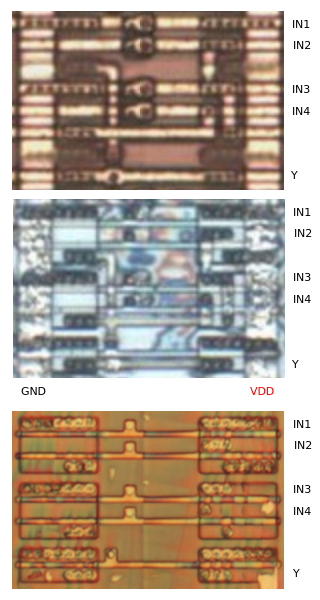

AO22

2-2 AND-OR two-level compound gate.

Name in DMG-CPU-Inside: AOI_MUX_2

|

|

Instances: APAG DOKY EDYF ELAF ETEF ETUP FARU FOLE FOPY GAFA GEJY HESU HETO HYTO JUFY KAHE KAVU KUPA (18 total)

AO222

2-2-2 AND-OR two-level compound gate.

Name in DMG-CPU-Inside: AOI_MUX_3

|

|

Instances: EVUG EZAG (2 total)

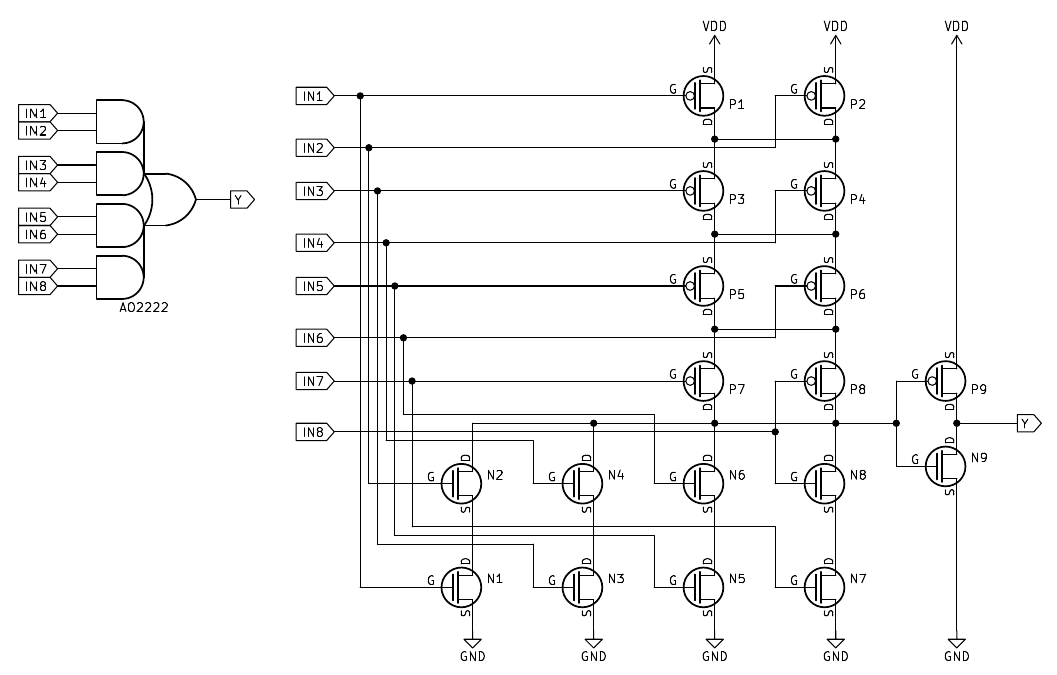

AO2222

2-2-2-2 AND-OR two-level compound gate.

Name in DMG-CPU-Inside: AOI_MUX_4

|

|

Instances: DARY DUNA ELYX EXES MOKA MUFA NELO NURA SUKO WALY WUFU (11 total)

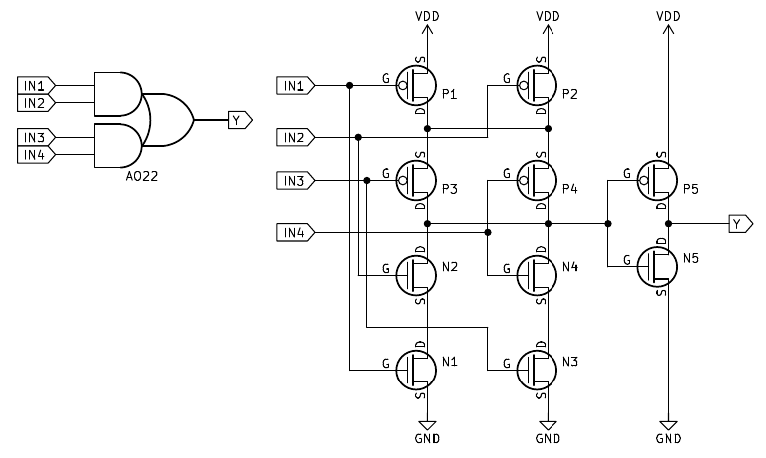

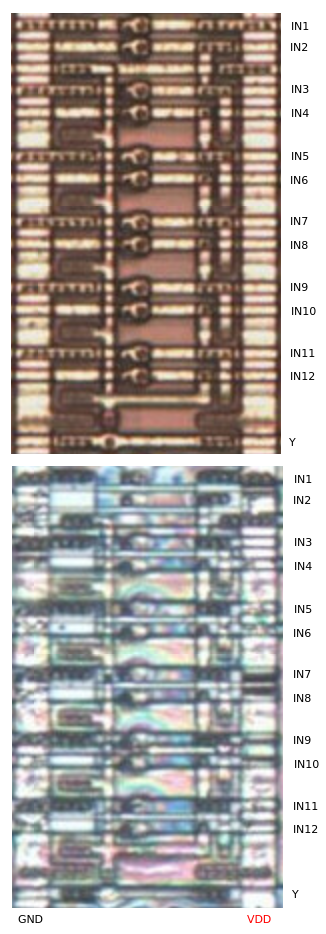

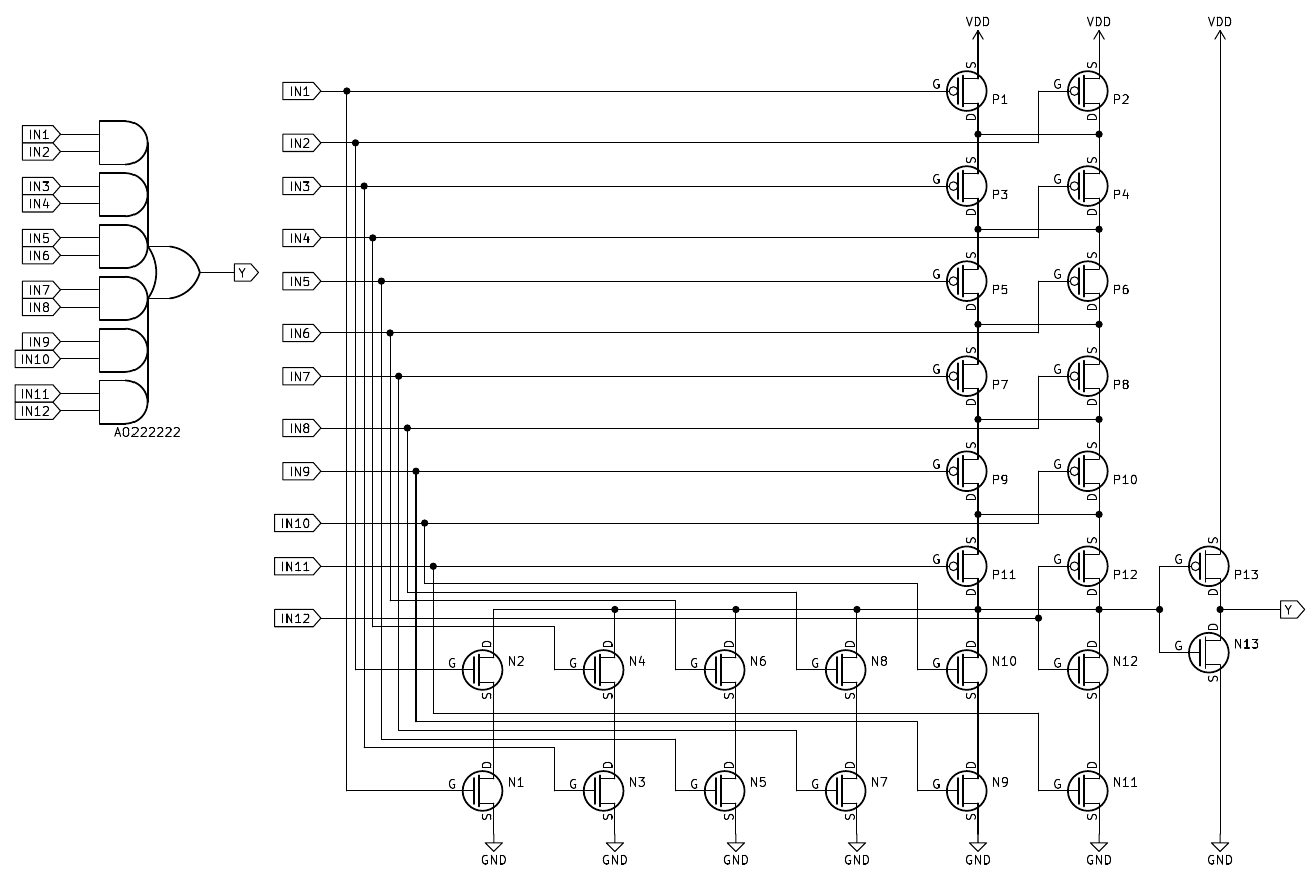

AO222222

2-2-2-2-2-2 AND-OR two-level compound gate.

Name in DMG-CPU-Inside: AOI_MUX_6

|

|

Instances: ETYR (1 total)

OAI21

2-1 OR-AND-INVERT two-level compound gate.

Name in DMG-CPU-Inside: NAO

|

|

Instances: CUFE (1 total)

OA21

2-1 OR-AND two-level compound gate.

Name in DMG-CPU-Inside: OA3

|

|

Instances: AGUT BYHA COHY DAJU DUMO DYBO DYLY EFAK EGUV EHUJ (10 total)

MUXI

Inverting multiplexer with two inputs.

|

|

Instances: CAVE COPO CUZO DATE DAZY KENA NYKU PETU RATO REFU ROKE SALA SOCE SYRU TECY TEKO UBAL UJYV UKAP (19 total)

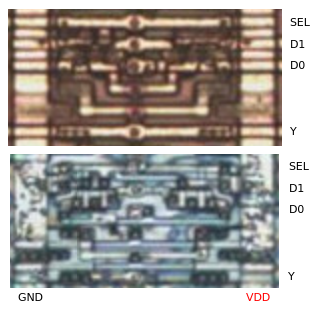

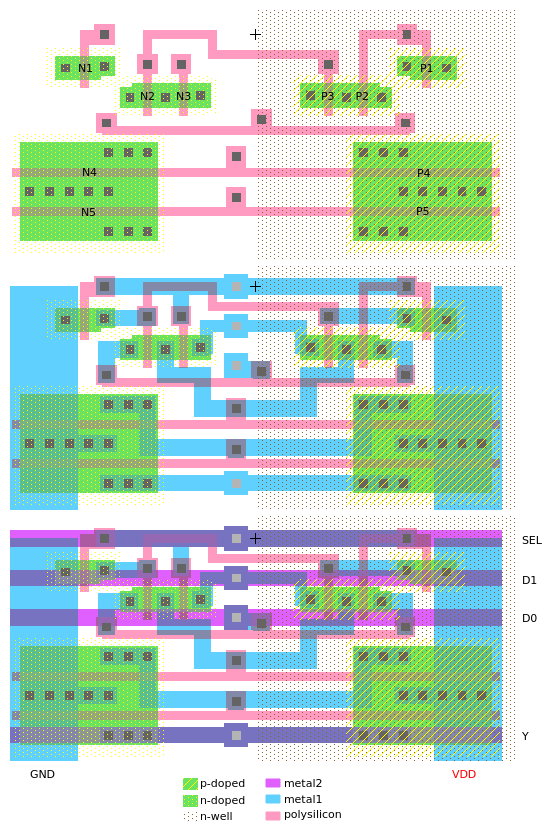

MUX

Multiplexer with two inputs.

|

|

Instances: AFUM AGYL AMER AMET APOK ASUR ATEM ATOL ATOV ATUR ATYR AXOL BENO BEZE BOLE BULE CELY EZUL FEME GALE MALE MANO MASU MOJY MUCE PACY PAMY PAWE PEGE PELO POBE PONO PUGU PULY PUTE RORU SALE TAZY TOLE TYHO TYJY ULUR (42 total)

Arithmetic gates

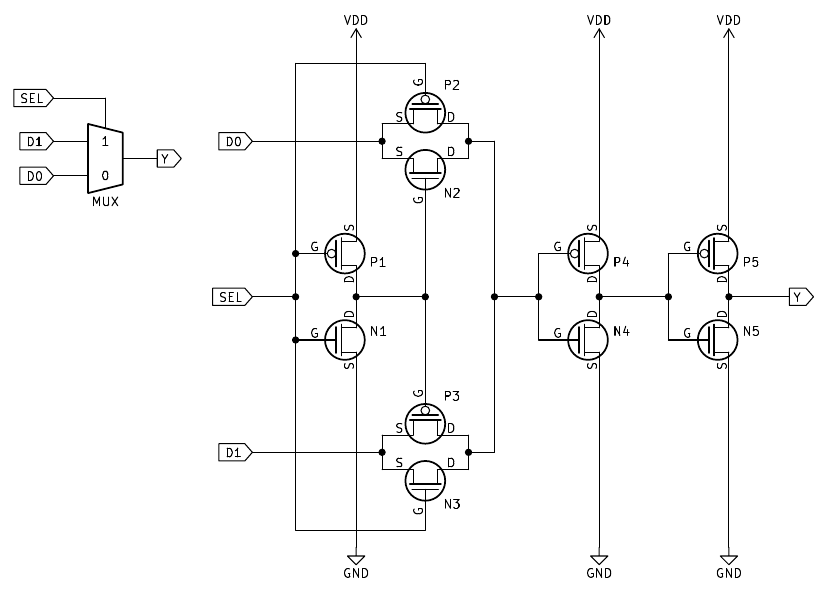

HALF_ADD

Half adder.

|

|

Instances: ATAD FAFO (2 total)

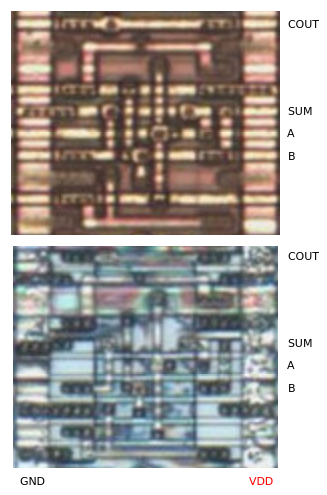

FULL_ADD

Full adder.

|

|

Instances: ABOD ACUL APYH BABE BEHU BEWY BYCA CORU DABA DOTO DULE DYXE ECAB EFYK EJOK EMUX ENEF ERUC ETAM ETEK FECO FEGO FUWA GEVA GOJU GOPU GUXA GYKY HALU HEXO JORY JULE WUHU (33 total)

Tri-state drivers

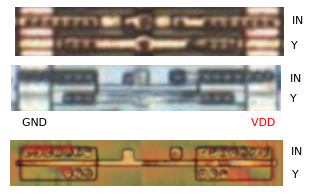

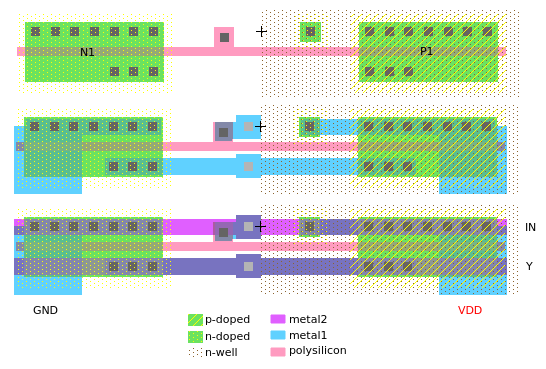

Tri-state inverters

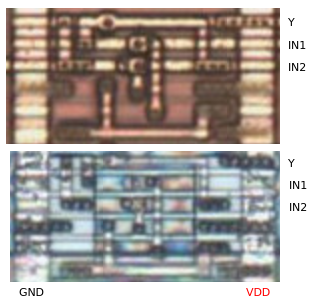

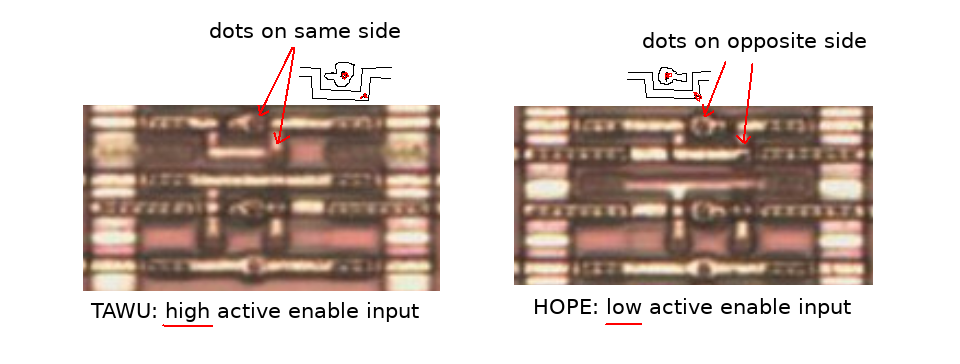

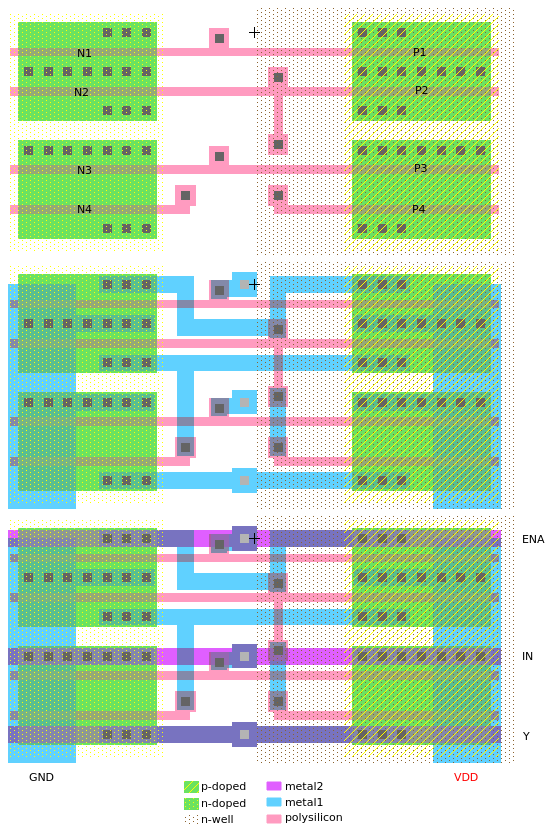

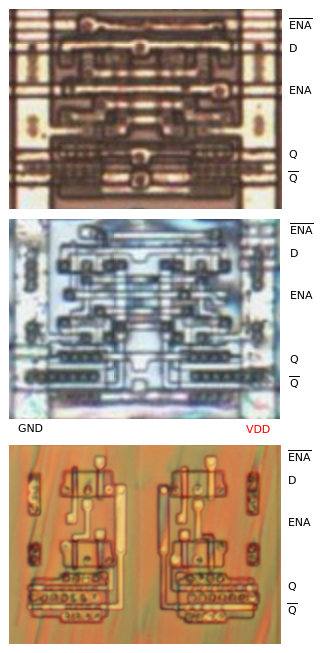

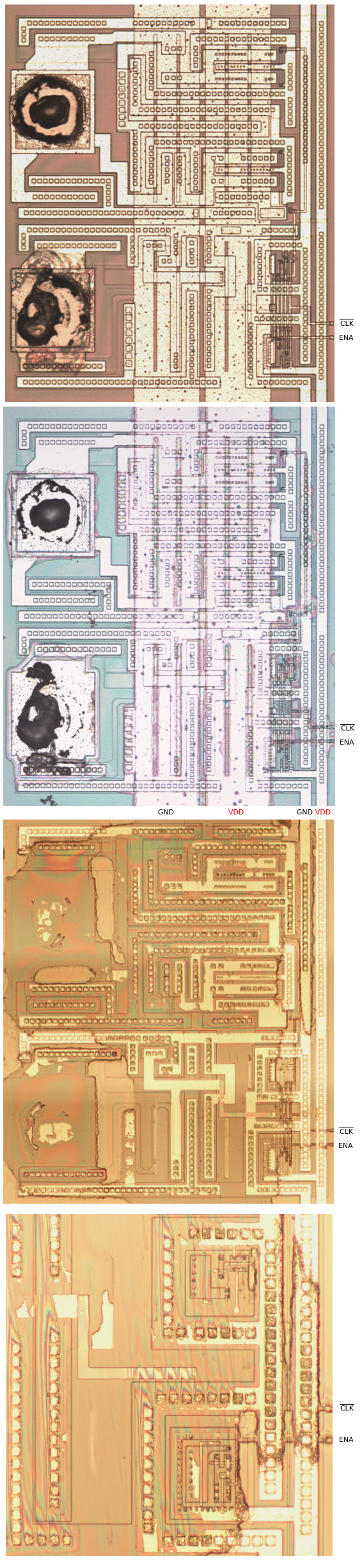

Tri-state inverters come in two very similar looking shapes: One has an active-high enable input; the other has an active-low enable input. This picture should help to identify them by highlighting the difference between the two:

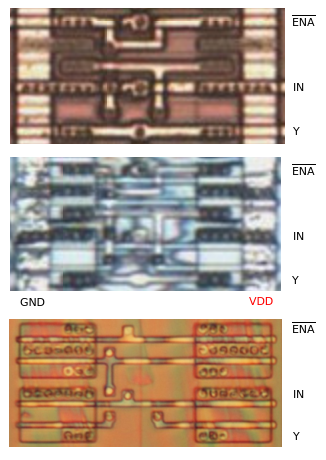

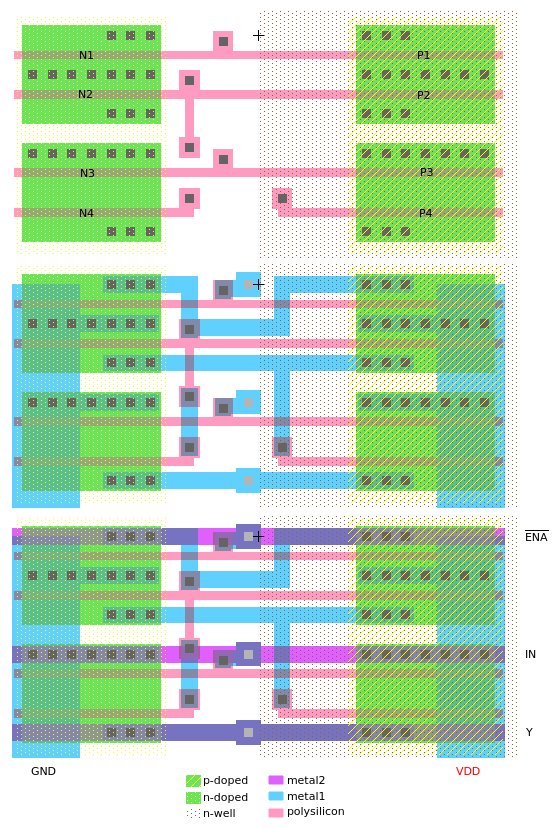

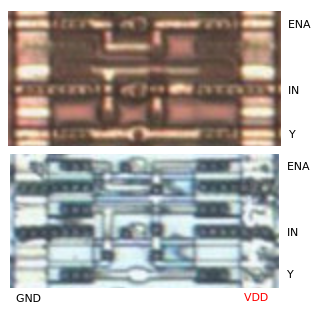

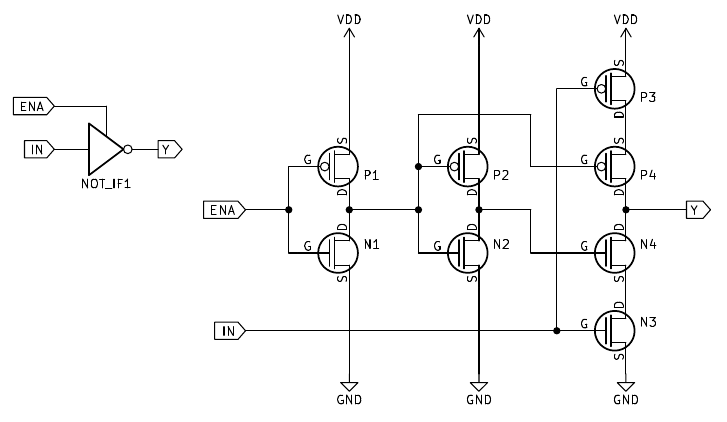

NOT_IF0

Tri-state inverter with active-low enable input.

|

|

Instances: ABEM ACOT ADYB AFEB AFEN AFOX AFOZ AGAG AGYK AHAC AHUM AJAL AJAN AJEC AKAJ AKOD AKUX AKYH ALEL AMAD AMUH AMUV AMYD ANOC ANUM APOB APOC APON APYV ARAR ARAS ARUX ARYN ASOX ASUM ASUZ ATAJ ATAX ATEL ATER ATUM AVEB AVEK AVUD AWAT AWED AWOS AXEC AXEM AXEP AXER AZOZ AZYP BACE BACO BAPE BASA BASY BAXE BAXU BAZU BEDA BEFE BEMO BENU BETU BETY BEVY BOCA BOCY BODU BOMO BOSO BOVE BOWO BUBO BUCE BUHU BUJA BUJY BUKY BUMA BUPY BUSE BUZU BYDO BYME BYNY BYPY BYRO BYTU CADA CAGA CAKO CAPU CASE CASY CATA CAVU CAWO CECY CEDU CEGA CEGY CEKA CELU CERE CETA CETU COCE COFO COHO COLY COTO COVE COXO CUBE CUBO CUCA CUCU CUDA CUDU CUDY CUGA CUJE CURY CUSA CUVU CUZU CYBY CYME CYPO CYRO DAFE DAHU DALO DALY DAMU DAVA DEMU DEMY DEXO DEZU DOBO DODE DONY DOPA DOWA DOXE DUHO DUVE DUZA DYGO DYNY DYSO ECAL EDOL EDOS EFUD EFUS EGEZ EKOB ELEP ELUG ELYC ENAP ERAF EREW ETAD ETEG EVAD EVAX EVYT EXYF EZOC FABY FACO FAGO FAJY FAKU FAMU FANA FAPY FARO FATE FAVA FEGU FERA FESA FETU FEVU FOBY FODO FORU FOSE FOTE FOZE FUGU FUGY FUHE FUSY FUTO FYDU FYKE FYKY FYZY GADU GAKA GAKY GAMA GARO GATE GAVO GAZO GECA GEDA GEFU GEFY GEGU GEKO GEMA GENE GERA GERO GOBA GOBY GODE GODO GODU GOFO GOJE GOJY GOME GONU GOSE GOTU GUNE GUSE GYBU GYKA GYPE GYZA GYZO HACA HACU HAMU HAPY HAVU HEDA HERE HEVE HEWA HOGE HONO HOPE HORO HOWU HUCO HUFO HUNA HUPE HUVU HYRE HYRY JACA JARO JEKE JEKU JEZA JOFO JOKU JUDE JUKE JURA JUVY JYNE JYSE KAFU KAKU KAMO KAMY KARY KEMA KESY KETA KOCE KOGE KORA KUMO KURO KUVE KYRO KYVU LACE LAJU LARY LEBA LELU LEPA LOBE LODE LODY LOKA LOLE LOVA LUGA LUKY LYCO LYKA LYZA MARA MEGA MELE MERA MOKO MUFE MUKA MULY PABA PELA PODA POFO POLO POTE PUFY PUNU PUZO PYGU RACE RARO RAZU REDO REDY RESE RETU RUMO RUSE RUVO RYKO RYMA RYNA RYSU SAFO SASY SEVU TAJU TAVO TEPE VACE VAFE VAHA VATO VAZU VEGA VEHA VEVY VEZA VOGU VOJO VOKE VOVO VULO VYNE VYTO WABA WABO WABU WACU WAGA WAJA WAKO WAMA WANA WAPE WARE WASA WATO WAVO WAWE WAXA WAXE WEHE WEJO WENU WEPY WERE WERU WEZA WEZE WOCY WOJY WOKO WOLU WONY WOWA WOXY WUCO WUDO WUJU WUKA WULE WUNE WUVA WUWE WUXE WUXU WUZU WUZY WYDA WYDU WYGA WYGO WYJU WYKY WYPO WYSE WYWY XAHE XAJU XAKY XAMO XARY XAWO XAXA XEBU XECA XEHE XEJA XERO XOBA XOBO XODY XOKE XONU XOPO XUBY XULO XUNO XUXU XYBO XYNE XYRA XYRE XYTO YBUK YHAL YJEM YKOZ YNEV YPOZ YRAD YVUC YWAV ZABY ZAJA ZAKY ZAMY ZARO ZATO ZAVE ZAXA ZECE ZEDY ZETU ZEXE ZOJY ZOPU ZOZO ZUDO ZUFE ZUFO ZUGA ZUKE ZUMO ZUMU ZYFA ZYPO ZYSU ZYTO (479 total)

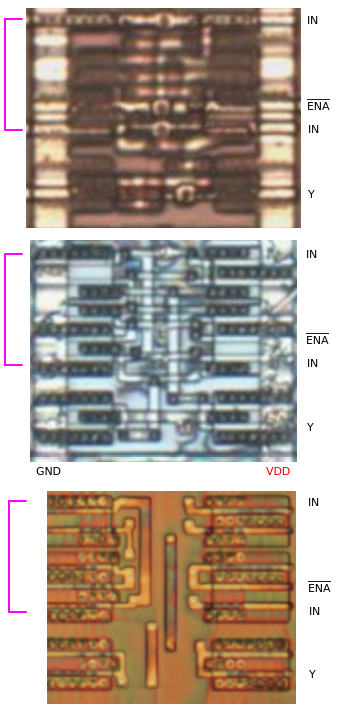

NOT_IF1

Tri-state inverter with active-high enable input.

|

|

Instances: BADE BATY BAVA BEZU BUNE CORE CUGY DAME DASO DESA DESY DETU DUDE DUGU EFAB ELUV ETAK EVOK NABO NELA NOLA NUVY PADO PANE PARE PEGY POLY PUSO PYRE RACY RAJU RAKU RALY RARU RASE RAVY REBA REJY REKA REMA REMO RESO RESU RETA REVA REXU ROCE RODY ROFO ROHA ROMY ROPU ROTA ROTE ROVA ROWE ROWU RUGA RUPY RUSA RYBU RYDO RYKE RYLA RYNE SALU SAPU SAWA SEGO SEPU SETE SEZU SOKU SOMU SOSY SOTU SUPE SUPO SURO SUVO SYPU TAKU TATU TAWU TEBY TEMU TOBO TOKU TUSE TYJA UPUG VAPY VEJY VURY WUGA (95 total)

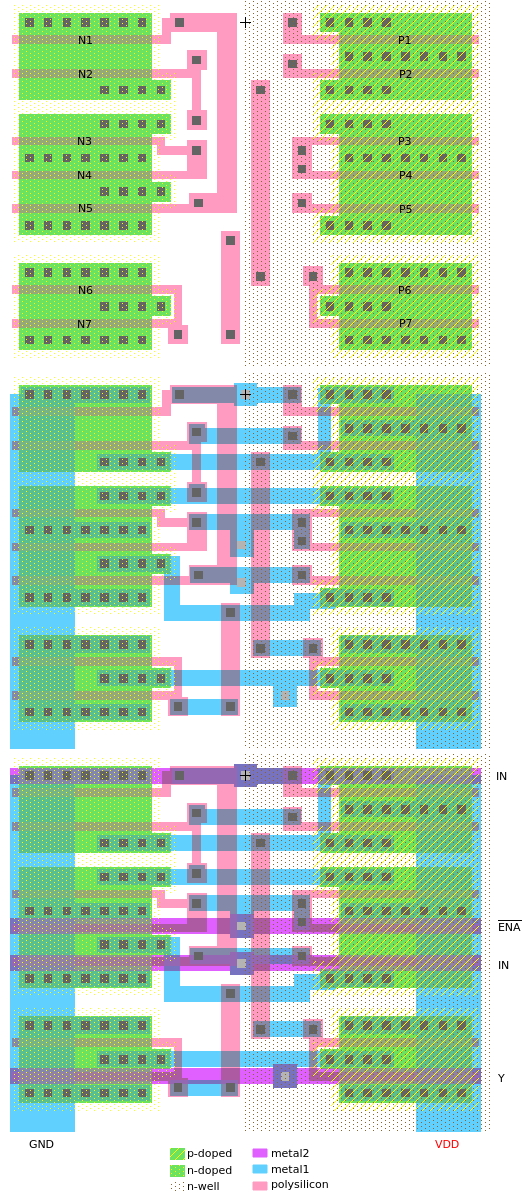

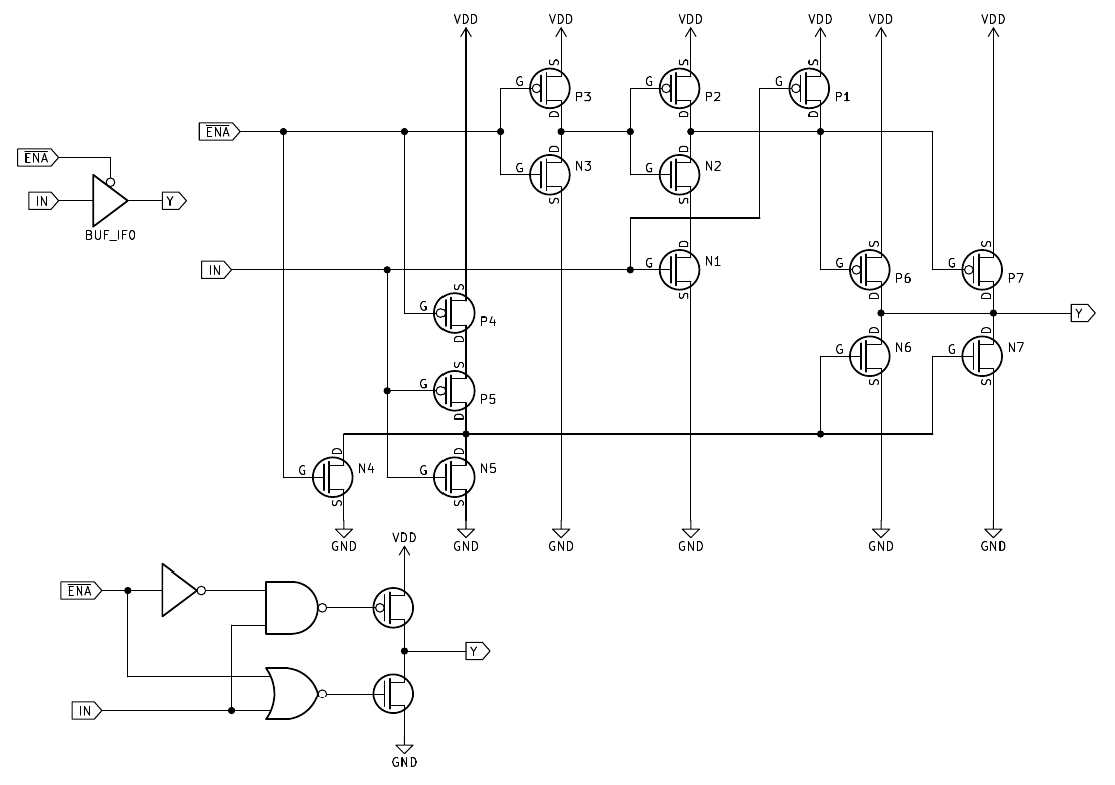

BUF_IF0

Tri-state buffer with active-low enable input.

The output of this cell has a higher driving strength, comparable to NOT_X2.

There is one external connection always made on this cell (see pink line in the picture) that is connecting the two IN inputs, even though they are connected internally on poly layer.

|

|

Instances: AJOV AKAN ANAR AZUV BYNA BYNE BYXE DEVE FYRA KEJO LEFY LOFA LORA LYNA MAPU NEFE RALA ROPA RUJO SAJO SEDU SEKE SOSA SOTE SUGU SUZA SYWA SYZU TAHY TAWO TAXO TAZU TEME TEMY TESU TEWA TEWU TOFA TOVU TUTE TUTY TYGO XABU XACA XAGU XELE XEPU XUNA XUVO XYGU YFAP YPON YTUX YWEG ZEHA ZYSA (56 total)

Storage elements

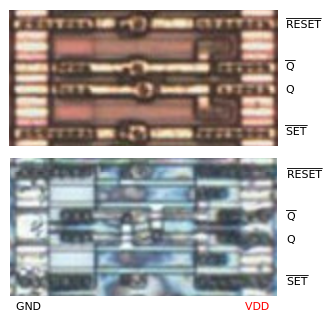

NAND_LATCH

NAND-latch with inverted set/reset inputs.

Name in DMG-CPU-Inside: AND2

Rgalland figured out the correct (NAND-latch) function of these cells.

|

|

Instances: BUTA FEMU GEXU GUGU JERY LONY TAKA (7 total)

NOR_LATCH

NOR-latch with set/reset inputs.

Name in DMG-CPU-Inside: OR2

Rgalland figured out the correct (NOR-latch) function of these cells.

|

|

Instances: ASOL BESU CYTO DALA DANE EROX FOZU FYFO GENA GOFY HAZO JEME KEZU LYXE POKY PYNU REJO ROXY RUPO TUBO WUJE WUSA XYMU (23 total)

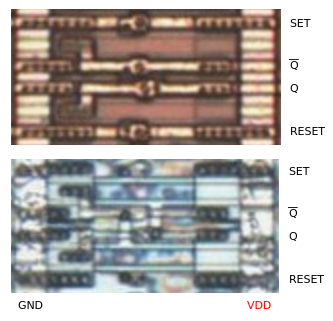

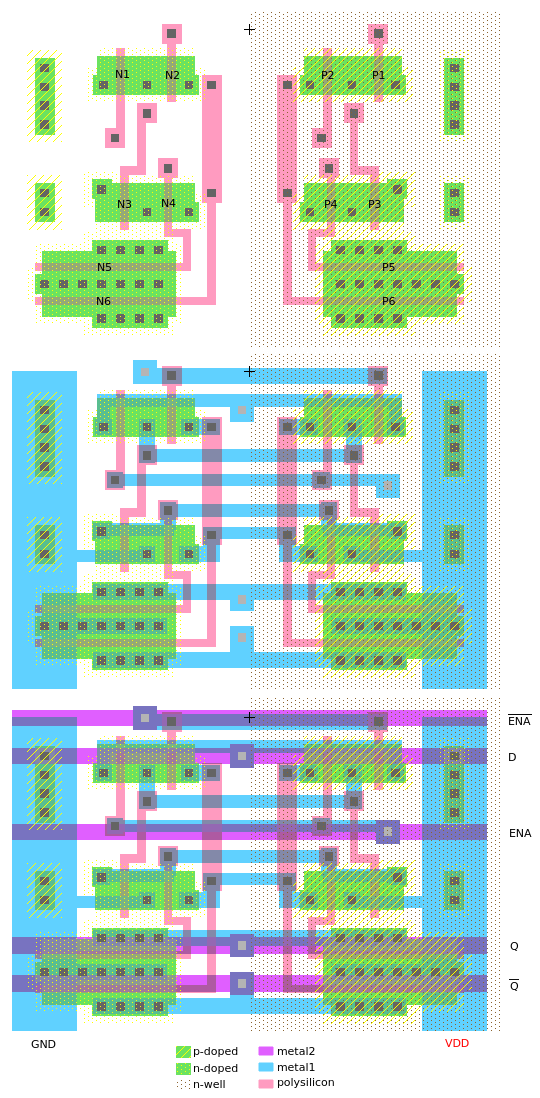

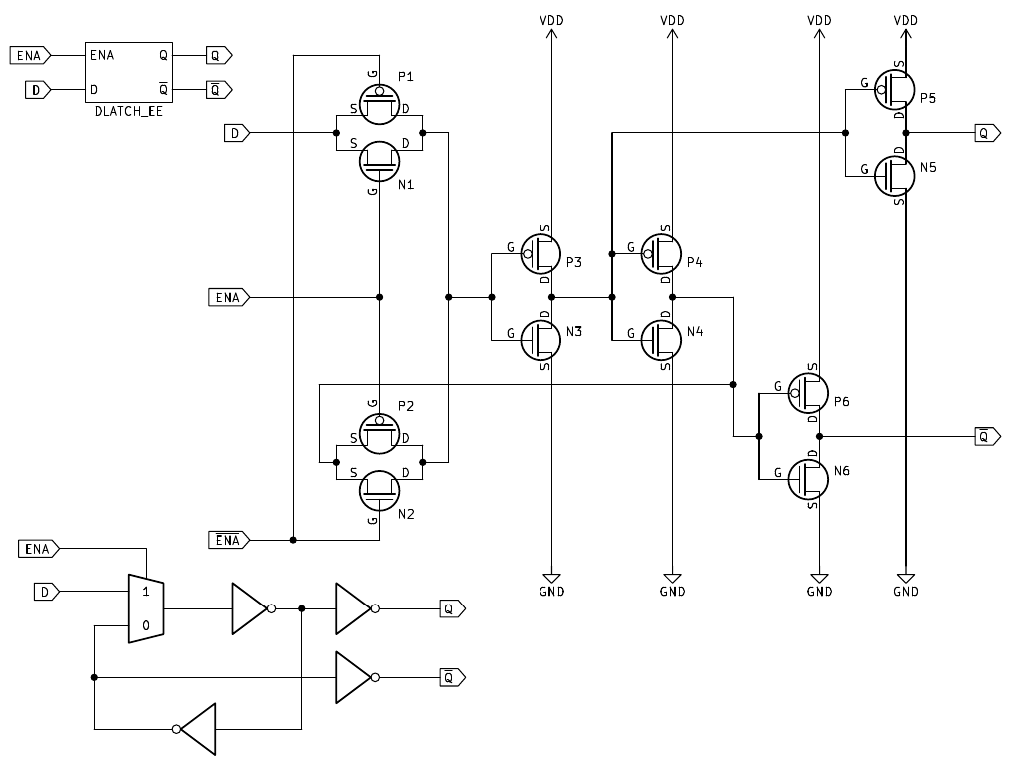

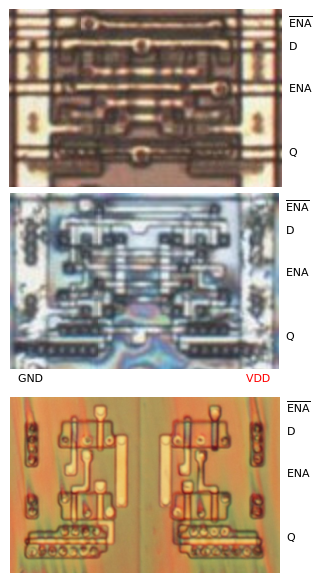

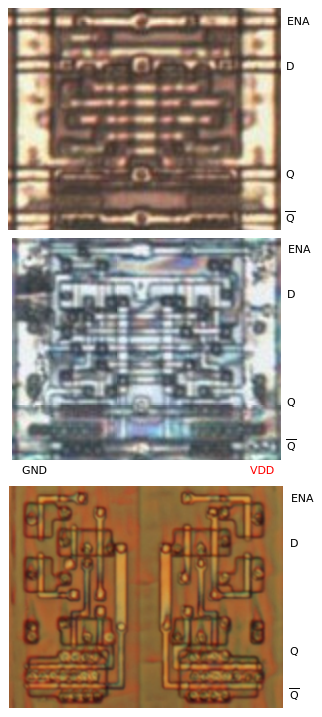

DLATCH_EE (A)

Gated data latch with externally inverted enable inputs.

There are two enable inputs to this cell. They need to be inverted towards each other. There is usually an inverter cell nearby that generates the inverted enable signal.

Name in DMG-CPU-Inside: DFF2

|

|

Instances: ABEG ABOP ABUG ABUX ACEP AFUT AFYM AFYX AMES ANED APEV AROF AXUV AZAP BADA BADO BAXO BECA BEXY BOXA BOZU BUHE BULU BUNA BYHE BYHU CADU CAJU CAJY CANA CAPO CEBO COMA CONO CUFA CUFO CUMU CUZA DAFU DEBA DEPO DESE DEVY DEWU DUHA DUNY DYSY EBEX EKAP EKOP ETAV ETYM FEFA FOFO FOGO FOXY FUZO FYHY FYSU GABO GACY GECU GESY GOHU GOMO GORU GULE GYHO GYNO LAWO LEPU LOSE LUGU LUNE LUXO MARU MAXY MENA MOGY MORU MOSA MOXY MUKE NAFA NUSY NYDO NYGY PARA PAVO POKU PULA PYLU PYNE WANU WYSO WYTE XABO XAKU XALO XANA XAVE XAZY XEFE XEGE XEGU XERU XOSY XOTE XOTU XOVA XUFO XUFU XUKY XUPO XUSO XUTE XYFE XYGO XYJU XYNA XYNU XYZE YBER YBOG YGUM YGUS YJEX YKUK YLOR YLOV YSOK YWAK YZAB YZEP YZOR YZOS ZAFU ZENE ZEXO ZEZY ZONY ZUBE ZUMY ZURO ZURY ZYLU ZYTY ZYVE (148 total)

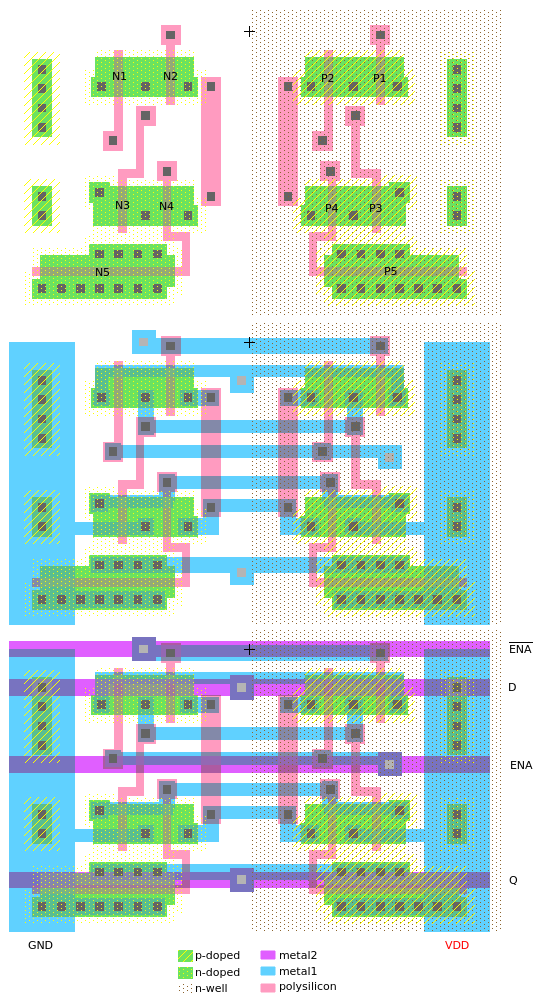

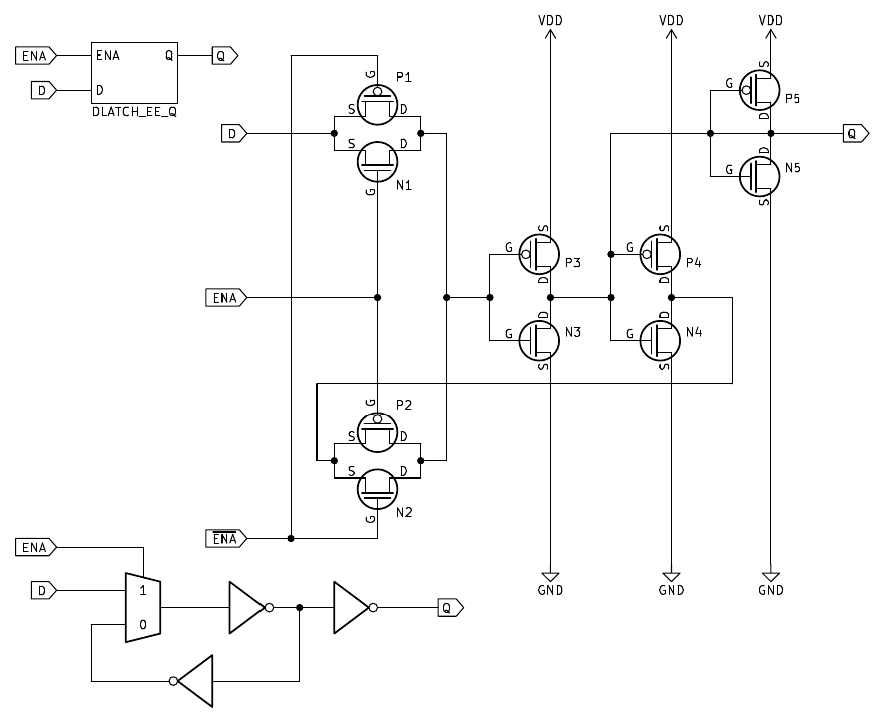

DLATCH_EE_Q (A2)

Gated data latch with externally inverted enable inputs and no inverted output.

There are two enable inputs to this cell. They need to be inverted towards each other. There is usually an inverter cell nearby that generates the inverted enable signal.

This cell type is very similar to DLATCH_EE, but it has no Q output and is one row shorter beacuse of that.

Name in DMG-CPU-Inside: DFF2

|

|

Instances: LEGU LUZO MEGU MOFO MUKU MYJY MYTU NASA NEFO NUDU PEBA PEFO PUDU RAMA RAMU REWO ROKA RYDU SAJA SEGA SELE SEMO SUNY SUTO (24 total)

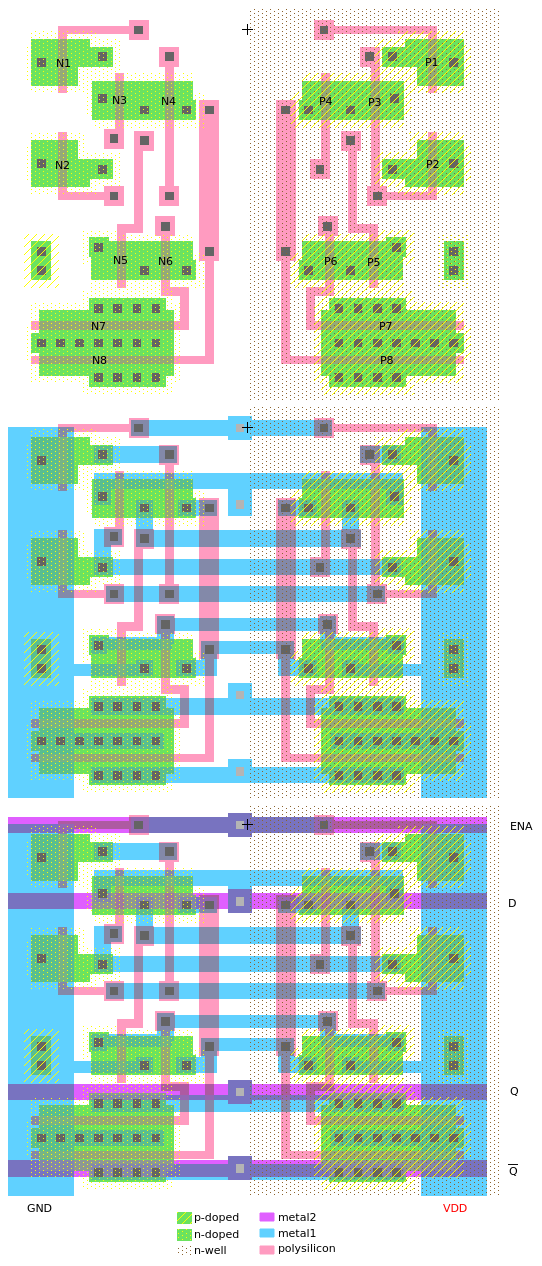

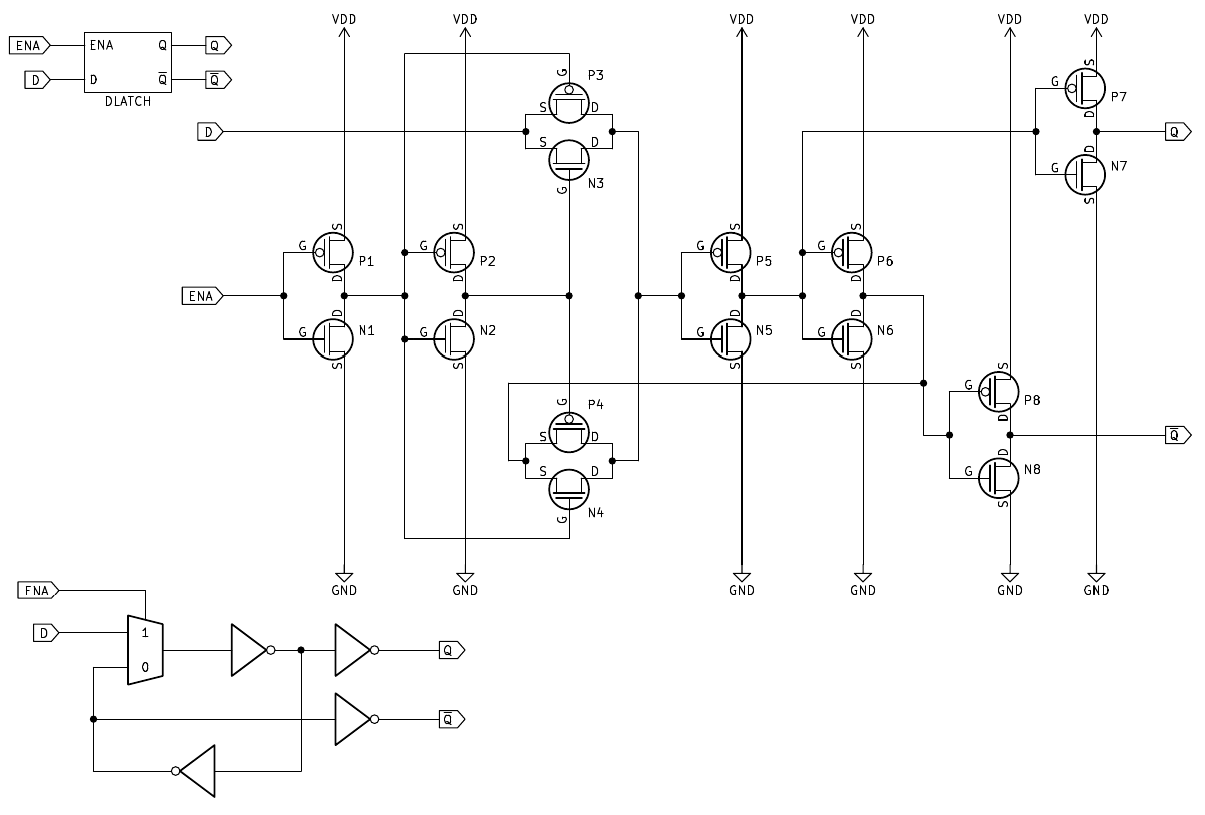

DLATCH (B)

Gated data latch with active-high enable.

Name in DMG-CPU-Inside: LATCH

|

|

Instances: ALOR ALYR APUR ARET AROS ARYM ATEV AVYS AWOB CYRA ECED KAPA KEJA KEVU KOLO LOBU LONU LUMY LUNO LYSA MATY MOPO NEJY NUTY NYRE PATE PAVY RAXY RONY RUPA SAGO SAZY SELO SODY SOMA WONE WYNO XAFU XYKY YCEB YDYV YRUM YSES YSEX YVEL ZAXE ZECA ZUCA ZUVE (49 total)

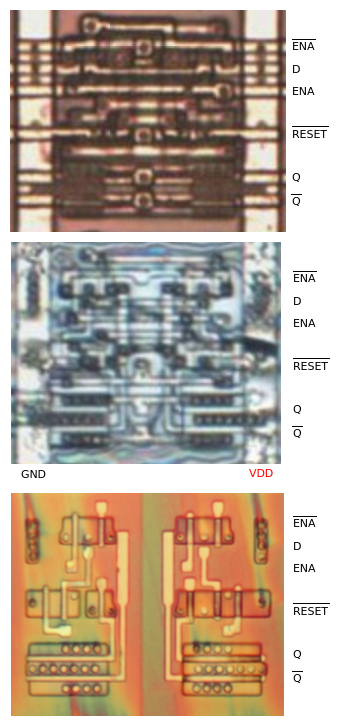

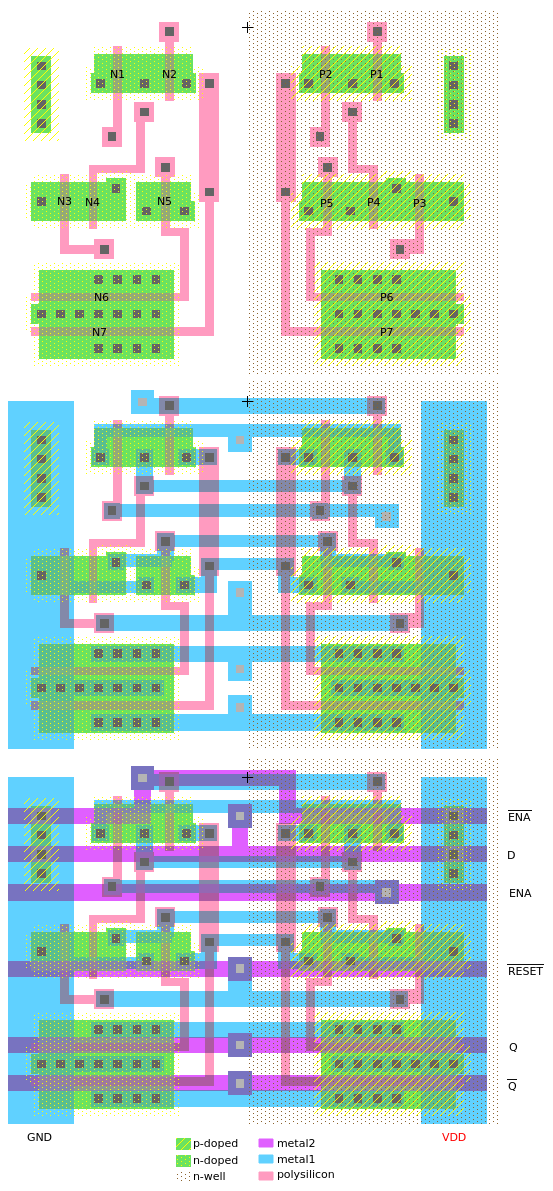

DRLATCH_EE

Gated data latch with externally inverted enable inputs and active-low reset.

There are two enable inputs to this cell. They need to be inverted towards each other. There is usually an inverter cell nearby that generates the inverted enable signal.

Name in DMG-CPU-Inside: DTFF

|

|

Instances: ADEK ADYK AFUR AGER ALEF ANAZ ANEV APEG APOS APUK ARAX ATUF AVAF BAFO BAKE BAMY BANA BANY BEDU BEFO BEGU BEMY BEPA BEPU BERA BOFA BOGU BOKO BORA BOTU BUDY BUME BUMO BYGA BYRE CABU CENA CESO CESY CEVO COZU CUNY CUSY CUVO CUVY CUZY CYFO CYWE CYXU DAKE DANY DATY DAZO DEDE DEPY DESU DUHY DUKO DUPE DURY DUZU DYBY DYCA DYFU EBOW EHYN EJUF EMER EMOK ENAD ENOR EPUM ERAZ EROL ETAP ETYJ EXUK EZUF EZYK FAXA FAXE FAZU FEDE FEDY FERO FESY FETA FEZU FOFE FOHA FOKA FOME FORA FORE FOTY FOVA FOZY FUBY FUJO FUNY FUSA FYCA FYMO FYTO FYTY GADY GAFO GAGE GARU GATA GAVE GAVU GAVY GAZA GEDU GEKY GODA GOGO GOKY GOXU GOZO GUBO GUFE GUMY GUPU GURA GUXE GYPU HAVA HODY HOGA HORE HOTO HUKY HYFU JACY JAFY JAKY JAMY JANY JARE JATY JAXA JAXO JEFE JEFU JEMO JENA JERO JETY JOMA JOPU JOVE JOVY JUPY JUSA JUZY JYPO KANA KOGA KOGU MEBY MELA MUVO MYCE MYPA MYPU NAFU NAGA NENE NESO NOFE NOKE NUKA NUKU NULO NYRO RAHA REFE ROXE RUFO RUGU SALO SEDY SOTA SYRY VAFA VEVO VUCE VYXE WECO WEDU WELO WEXU WOKY WOTE WUHA WYDE WYMO WYNA XABE XAFO XAKO XECY XEKA XEPA XEPE XERE XEXA XOMY XONA XOLY XUNY XURY XUVY XUZO XYBA XYLO XYMO YBED YCOL YGAJ YLAH YMEM YNEP YPOD YRAC YROP YVAG YZOF ZALA ZECU ZESA ZOGO ZOLA ZOLY ZULU ZYJO (238 total)

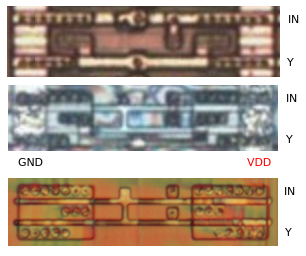

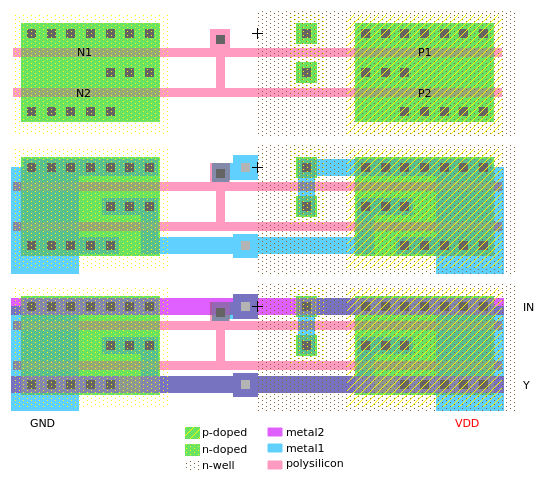

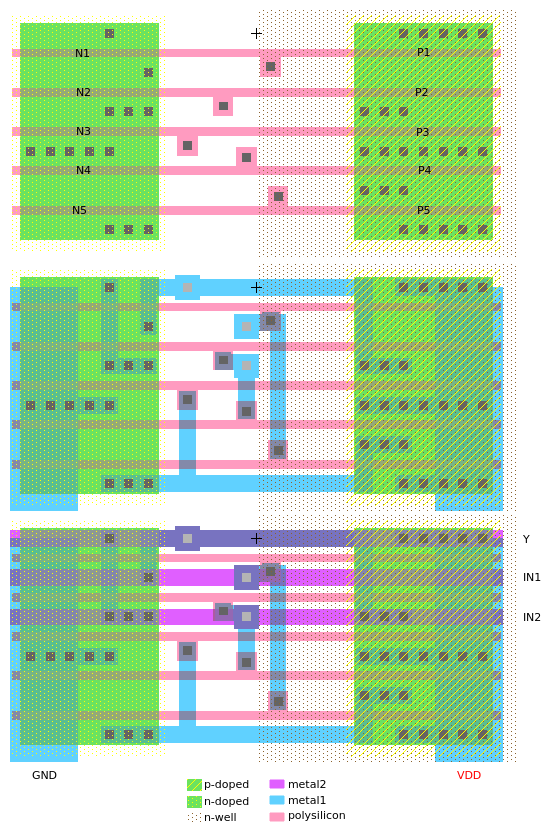

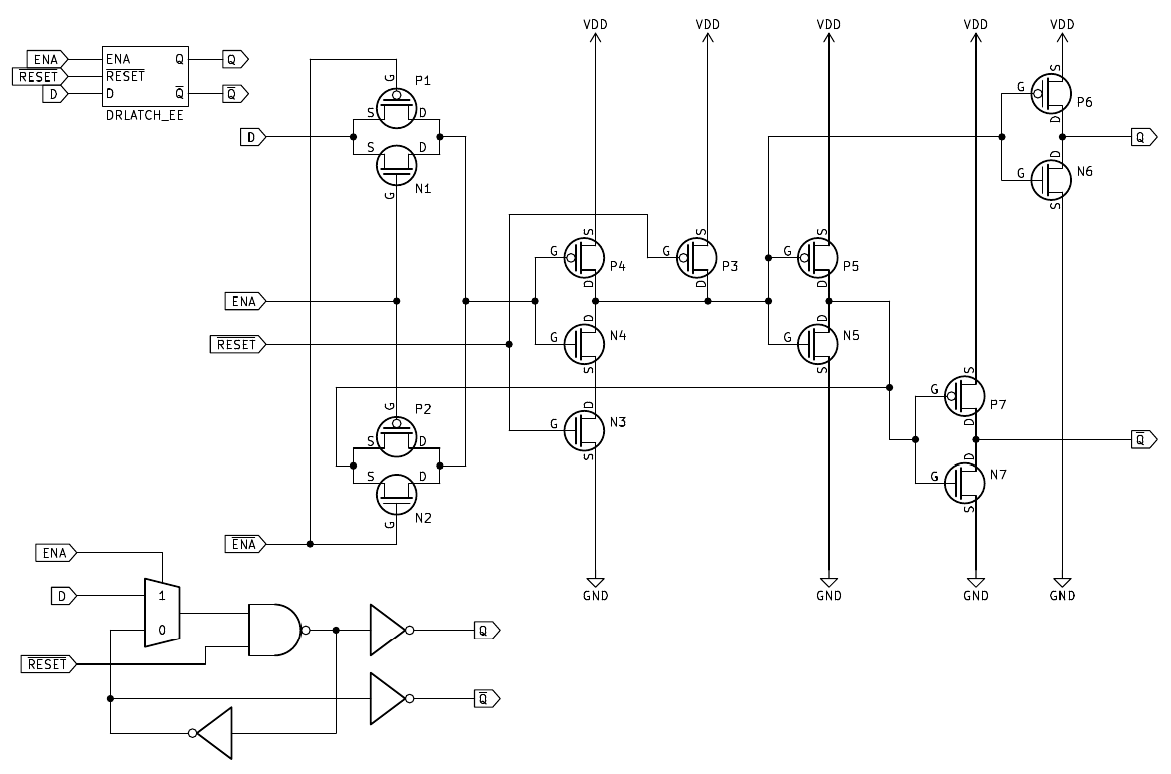

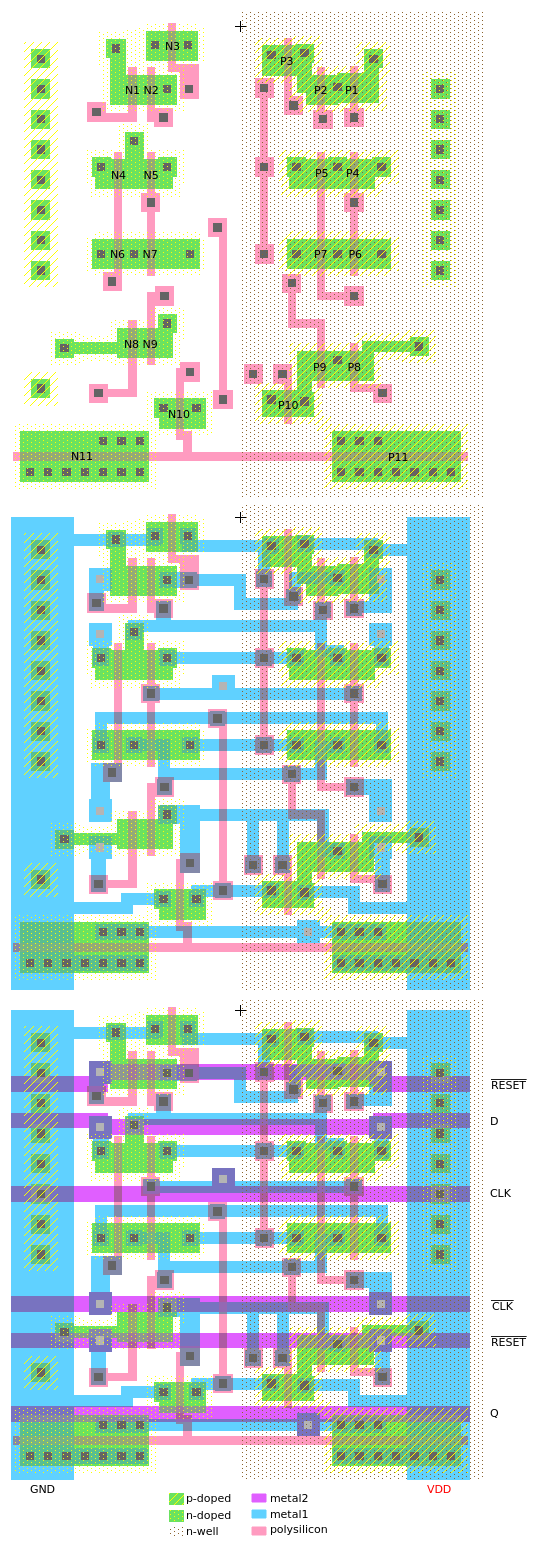

DFFR_CC_Q (A)

Single-edge-triggered data flip-flop with complementary clock inputs, active-low asynchronous reset, and no inverted output.

There are two clock inputs to this cell. They need to be inverted towards each other. There is usually an inverter cell nearby that generates the inverted clock. The flip-flop triggers on a positive edge of CLK and a negative edge of CLK.

There is one external connection always made on this cell (see pink line in the picture) that is required to connect the two RESET inputs.

This cell type is similar to DFFR_CC, but it is missing the Q output. Furthermore, it is one row shorter.

Name in DMG-CPU-Inside: DTFF

|

|

Instances: DEFA DELE DEVA DEXE DOFY DOLY EDOK EPYR ETER EXAP FAXO GALO GELE GYME HELE HOPA HORA JAPE JETE JODE JYME KARE POJU POWY POXA POZO PULO PYJU PYZO RAWU (30 total)

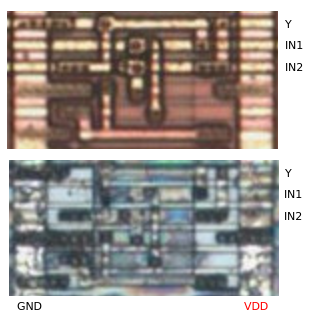

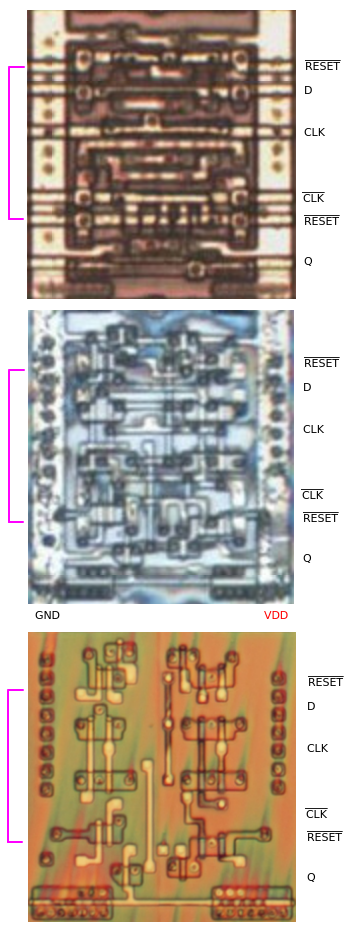

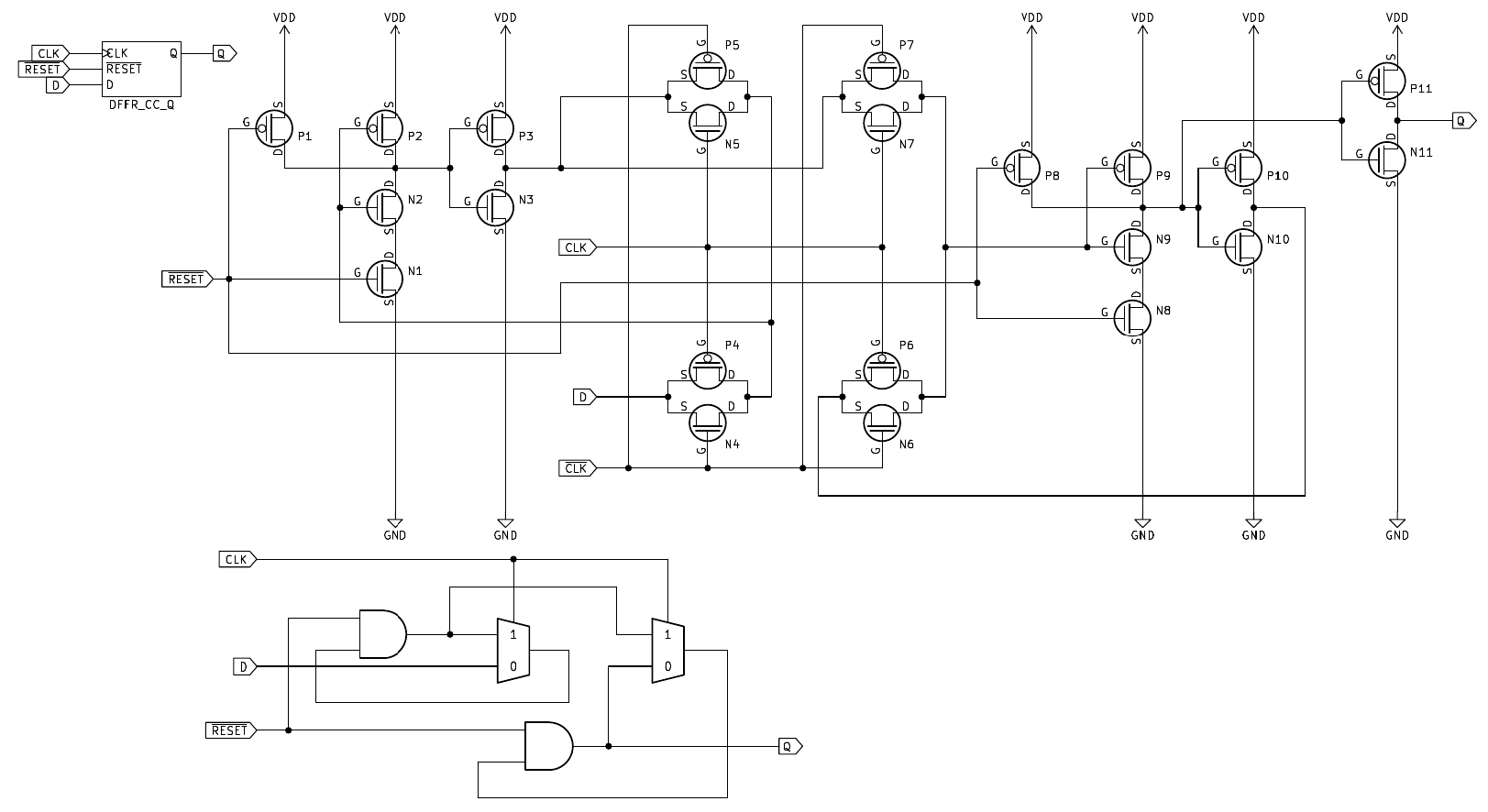

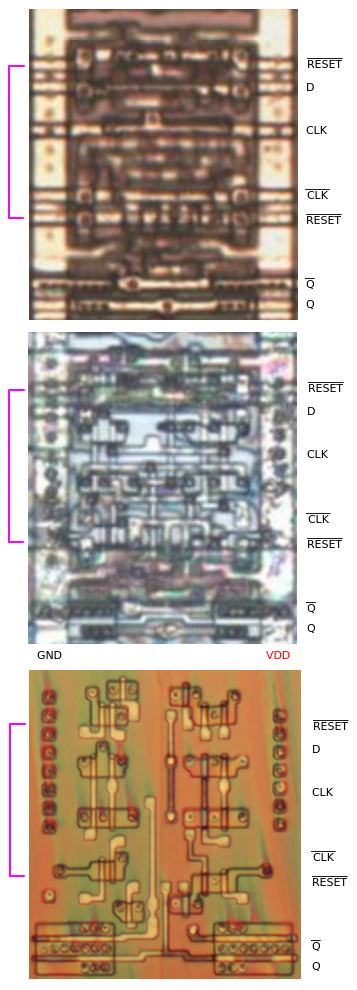

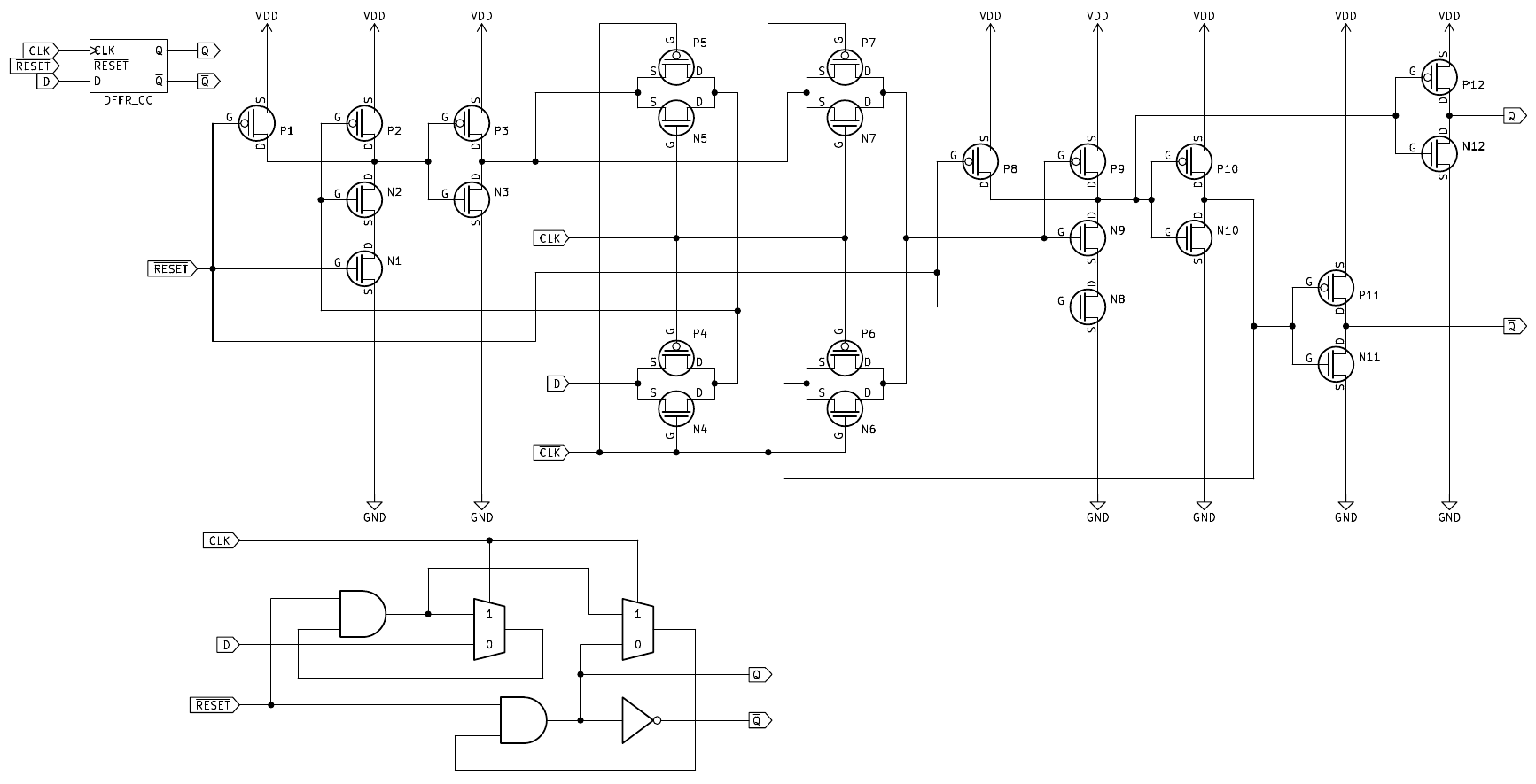

DFFR_CC (B)

Single-edge-triggered data flip-flop with complementary clock inputs and active-low asynchronous reset.

There are two clock inputs to this cell. They need to be inverted towards each other. There is usually an inverter cell nearby that generates the inverted clock. The flip-flop triggers on a positive edge of CLK and a negative edge of CLK. Sometimes the clock inputs are driven by the Q and Q outputs of another flip-flop of the same variant.

There is one external connection always made on this cell (see pink line in the picture) that is required to connect the two RESET inputs.

Name in DMG-CPU-Inside: DTFF

|

|

Instances: AFER CAGY DAPE DYVE EROS XADU XECU XEDY XOBE YDUF ZUZE (11 total)

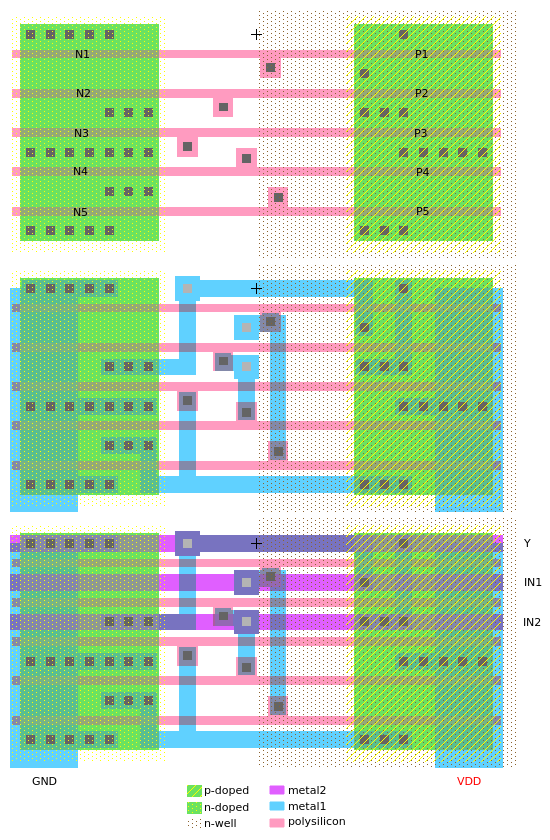

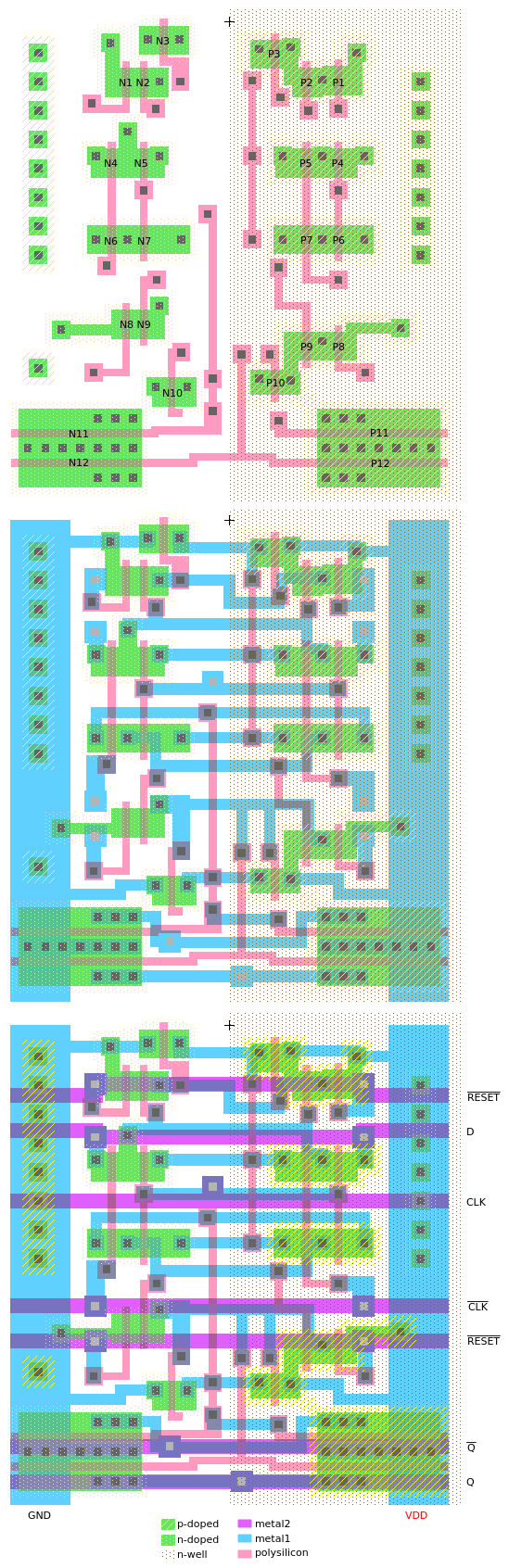

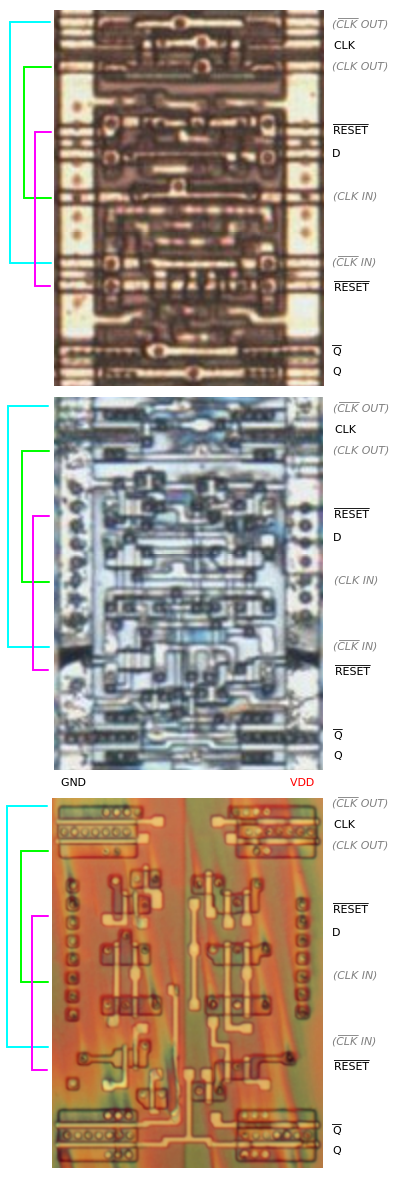

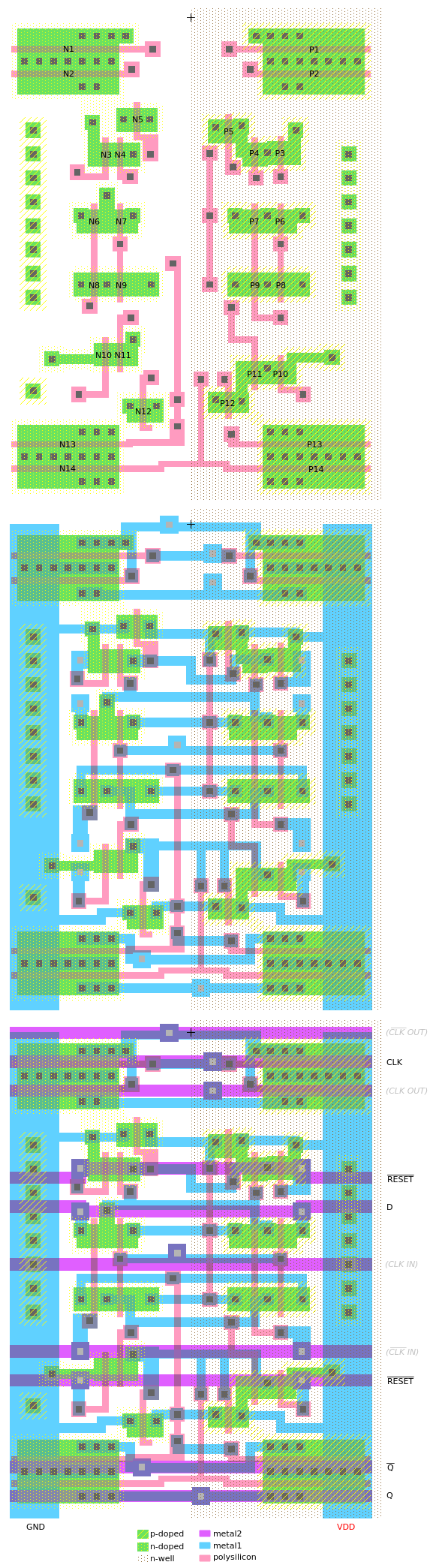

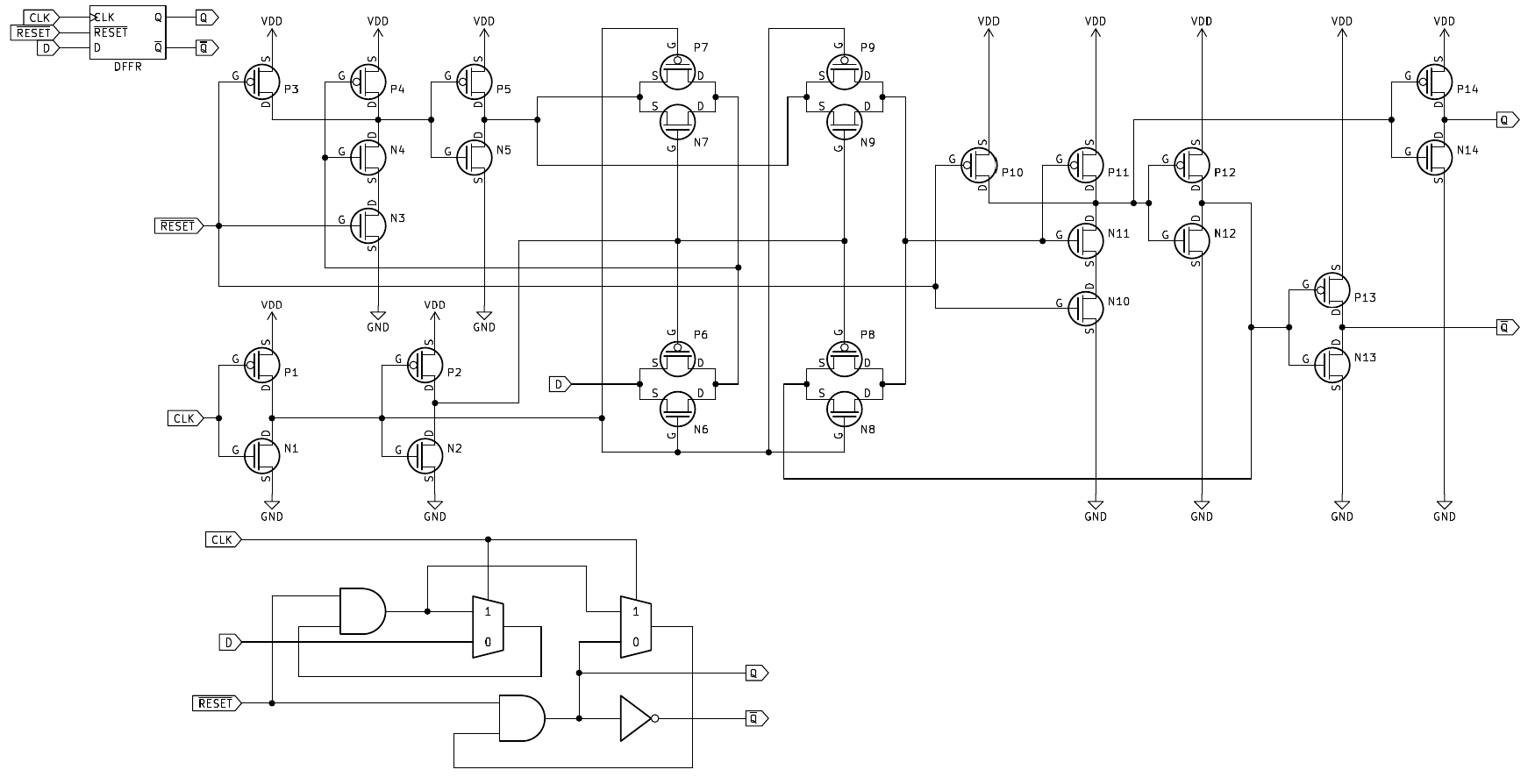

DFFR (B2)

Positive-edge-triggered data flip-flop with active-low asynchronous reset.

This cell is basically the same as DFFR_CC but with an extension at the top. This extension inverts the clock signal twice to regenerate a possibly degraded clock and to provide the complementary clock in the process.

There are three external connections always made on this cell (see cyan, green and pink lines in the picture). The cyan and green connections feed the positive and negative clocks generated by the extension to where they would be connected to if this was a cell of variant B without extension. There is not a single instance of this cell that has those two clock connections crossed, which means all instances trigger on a positive clock edge. The pink connection is required to connect the two RESET inputs.

Name in DMG-CPU-Inside: DTFF

|

|

Instances: ABEL ACEF AGEM AJER AMUT ANEL APUG ATEP ATYK AVOK AZET AZUS BANO BARA BATU BAZA BEGO BESE BEXA BOWY BURO BUSA BYBA BYLU BYTE CAFA CALO CALY CANO CARU CATU CAZA CEDY CEMO CENO CERO CERY CEXO COFY COMY COTY CULY CUXY CYDE CYLO CYRE DALE DAVO DEKO DEMO DERE DETE DEZY DOBA DOKE DOME DOPE DORY DOSE DOTA DURE DUWO DYBE EBOJ EFAL EFAR EFUZ EGAV ELOX ELYN ELYS EPOR ERUS ERUT ESEP ESUT ETAF EXEL EXUQ EZEC EZEF FAHA FARE FEKU FETY FEXU FOBA FONO FONY FOSY FUGO FYNO FYTE GARA GARY GATY GONE GORA GOSO GOTA GYKO GYRA GYSU GYTA HADA HAPE HENO HEPA HEPO HEZU HORY HUNO HYRO JAJU JALE JAVO JEPE JESO JOPA JOTO JUTE JUXE JYNA KALY KECY KELY KERU KETU KOMU KOZY KUKO KUTA KUZY KYME KYNO KYWY LAFO LAXU LEBE LEMA LENE LEXA LOVU LOVY LUCA LUVY LYDO LYZU MAKA MATO MATU MEDA MESU MOBA MUGU MURU MUTY MUWY MYTA MYTE MYRO NAKY NAPO NEFY NOPA NUNU NUTO NYDU NYKA NYKE NYKO NYPE NYVA NYZE PAHO PETO POPU PORY PUXA PYCO PYGO PYLO PYRO RENE ROGA ROPO RUBU RUTU RYFA RYKU SABO SABU SAMY SARY SAVY SAXO SEBA SETA SOBU SOLA SOPU SOTO SOVY SUBU SUDA SUDE SUFY SYBE SYGU TAHA TAKO TAMA TATE TAXA TEKA TEKE TELU TERO TERU TESE TEPU TOBU TOFE TOZO TOXE TUFU TUGO TUHU TUKY TULU TULY TYFO TYPO TYRU TYRY TYVA UFOR UGOT UKET UKUP UNER UNYK UPOF VENA VOGA VONU VUJO VYMU VYNO VYZO WAFY WAPO WEWY WOBO WODY WOMY WOSU WUVU WYKA WYKO XEHO XODU XOLO XUDY XUVA XYDO YFEL (267 total)

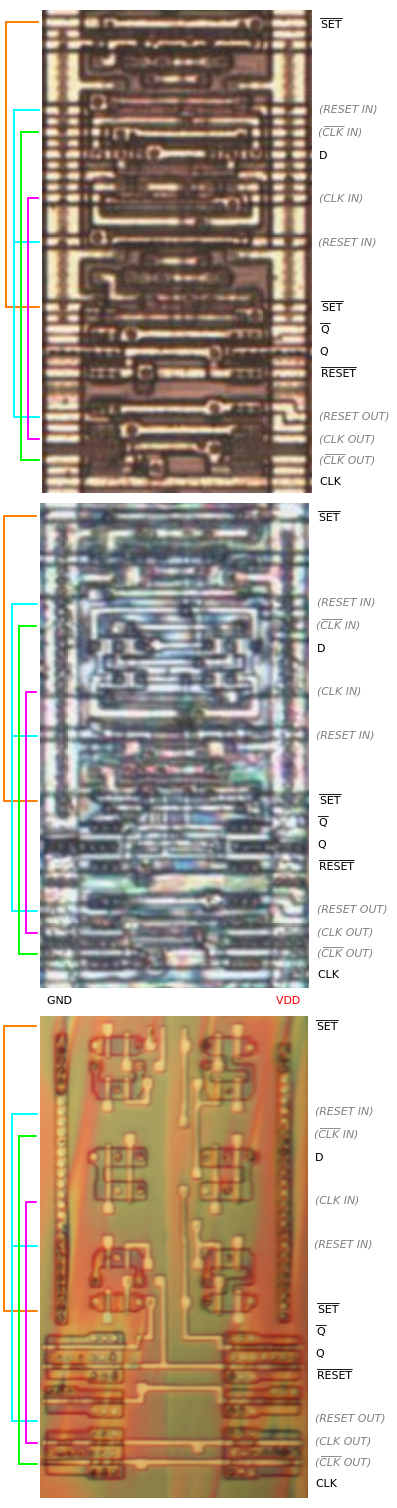

DFFSR

Positive-edge-triggered data flip-flop with active-low asynchronous set and reset.

There are five big inverters at the bottom of the cell. Two of them are inverting the clock signal two times to regenerate a possibly degraded clock and also to provide the complement clock in the process. The third one is used to invert the RESET signal. The cell doesn't internally connect the outputs of these three inverters anywhere. There are external connections needed to be made to connect them to the rest of the cell. The other two inverters are driving the Q and Q outputs.

There are four external connections always made on this cell (see orange, cyan, green and pink lines in the picture). The green and pink connections feed the positive and negative clocks generated by the bottom part to the transmission gates in the main part of the cell. There is not a single instance of this cell that has those two clock connections crossed, which means all instances trigger on a positive clock edge. The cyan connection feeds the reset signal from the bottom part to the AOI compounds in the main part of the cell. The orange connection is required to connect the two SET inputs.

Name in DMG-CPU-Inside: DFF3

|

|

Instances: AXAN AGEZ BEKU CUBA DEGU DOJO DOVU DYGY DYRA EDER EDUL EJAB ELUX EROD EVAB EXAC FABU FEDO FELY FUDE GOGA HAVO HOLU HOPO HYKA HYXU JEFA JOLU JOTA JYKA LALU LEFE LESU LOPE LYME MACU MASO MODA MODU MOJU MYDE NATY NEDA NEPO NOZO NUKE NURO NYBO NYLU PALU PEFU PYBO PYJO RALU ROSA RUGO RYSA SADY SATA SETU SOBO SOHU SOMY TACA TOMY UBUL ULAK VAFO VANU VARE VAVA VEZO VOSA VUMO VUPY WEBA WODA WORA WUFY WURU WYFU WYHO XETE (83 total)

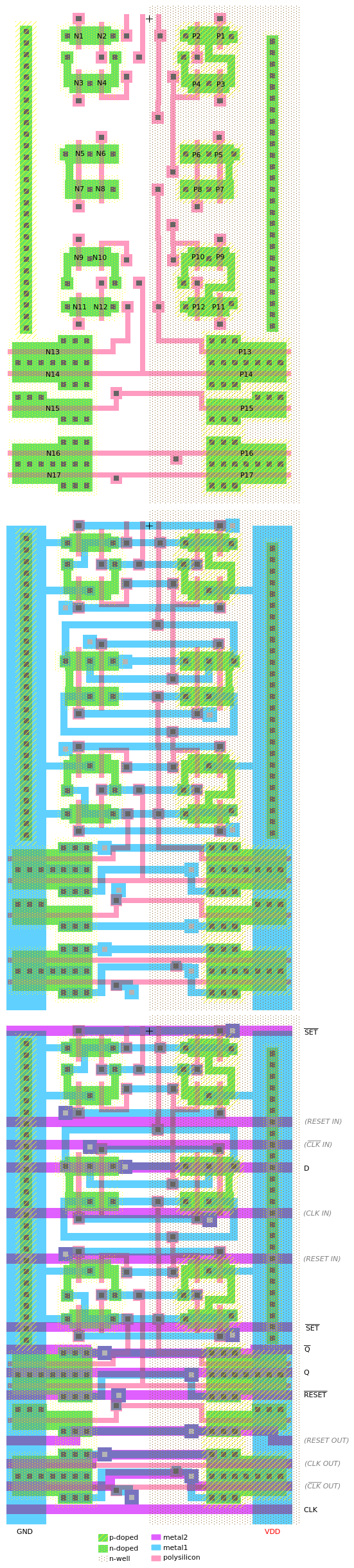

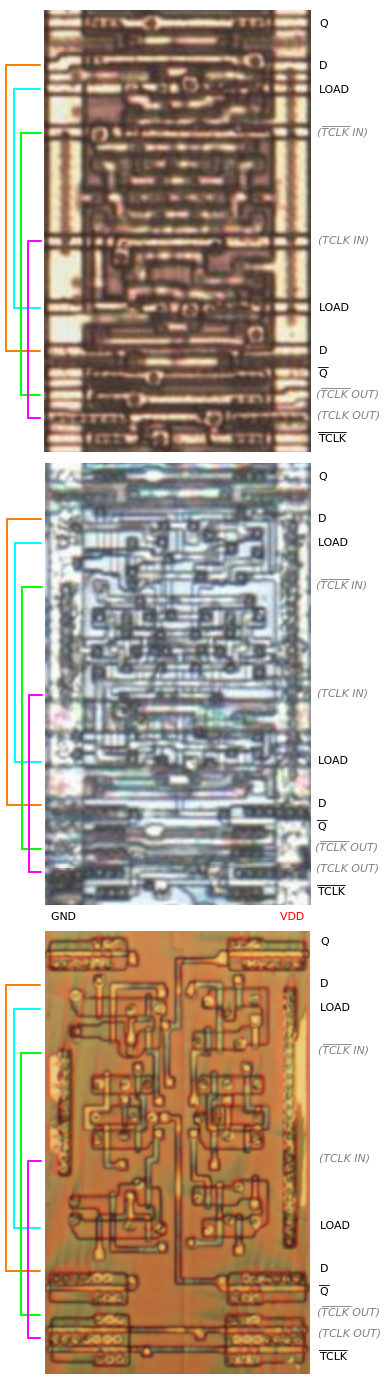

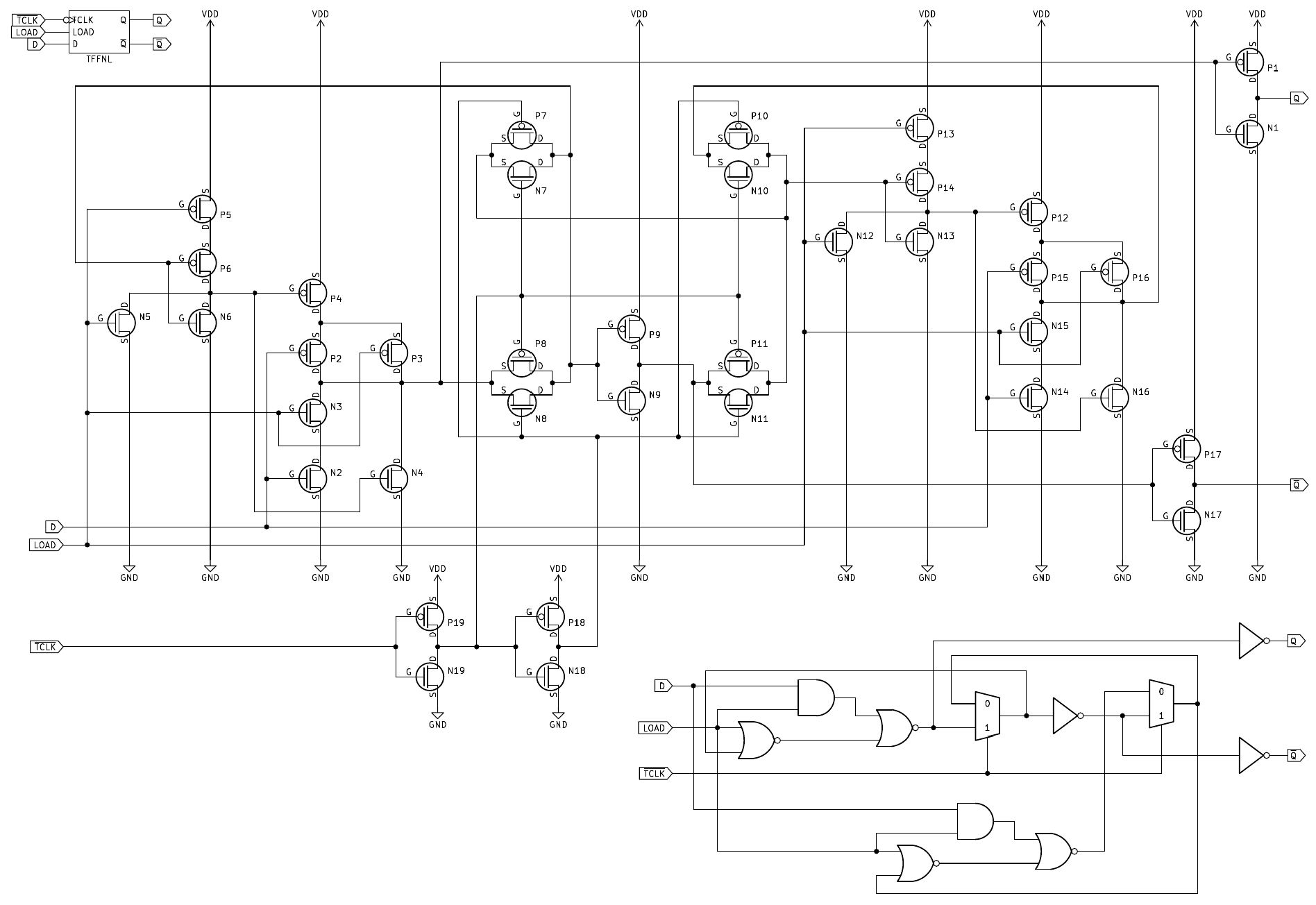

TFFNL

Negative-edge-triggered toggle flip-flop with active-high asynchronous data load.

This flip-flop is used for counters that can be loaded with a value.

There are four external connections always made on this cell (see orange, cyan, green and pink lines in the picture). The green and pink connections feed the positive and negative clocks generated by the two inverters at the bottom of the cell to the transmission gates in the center. There is not a single instance of this cell that has those two clock connections swapped, which means all instances trigger on a negative clock edge. The orange and cyan connections are required to connect the two D and the two LOAD inputs respectively.

Name in DMG-CPU-Inside: COUNT

|

|

Instances: AKYD BACY BOVY BUVA BYRA CAJA CAME CAVY CAXY CEDO CERA COFE CONU COPA COPU CUNA CUNO CUPO CURA CYPU CYVO DANO DENA DOGO DONE DYNU EDOP EKOV EMUS ERAM ERYC EVAK EZOF FATY FAVE FAVY FEKO FENA FENO FERU FETE FEVA FOMY FORO FORY FUXO FYLO FYRO FYRU GANE GANO GAPO GATU GAXE GEMO GEVO GOCA HAFO HEMY HEPU HERO HEVO HEVY HOKO HYFE HYKE JAPU JEMA JEVY JONA JORE JOVA JYCO JYFU JYRE JYTY KAFO KEJU KEMU KENO KENU KEPA KERA KEZA KUNU KUPE KUTU KYGU KYNA NUGA PEDA PERU POVY RAGE RATE REGA RUBY (97 total)

I/O pads

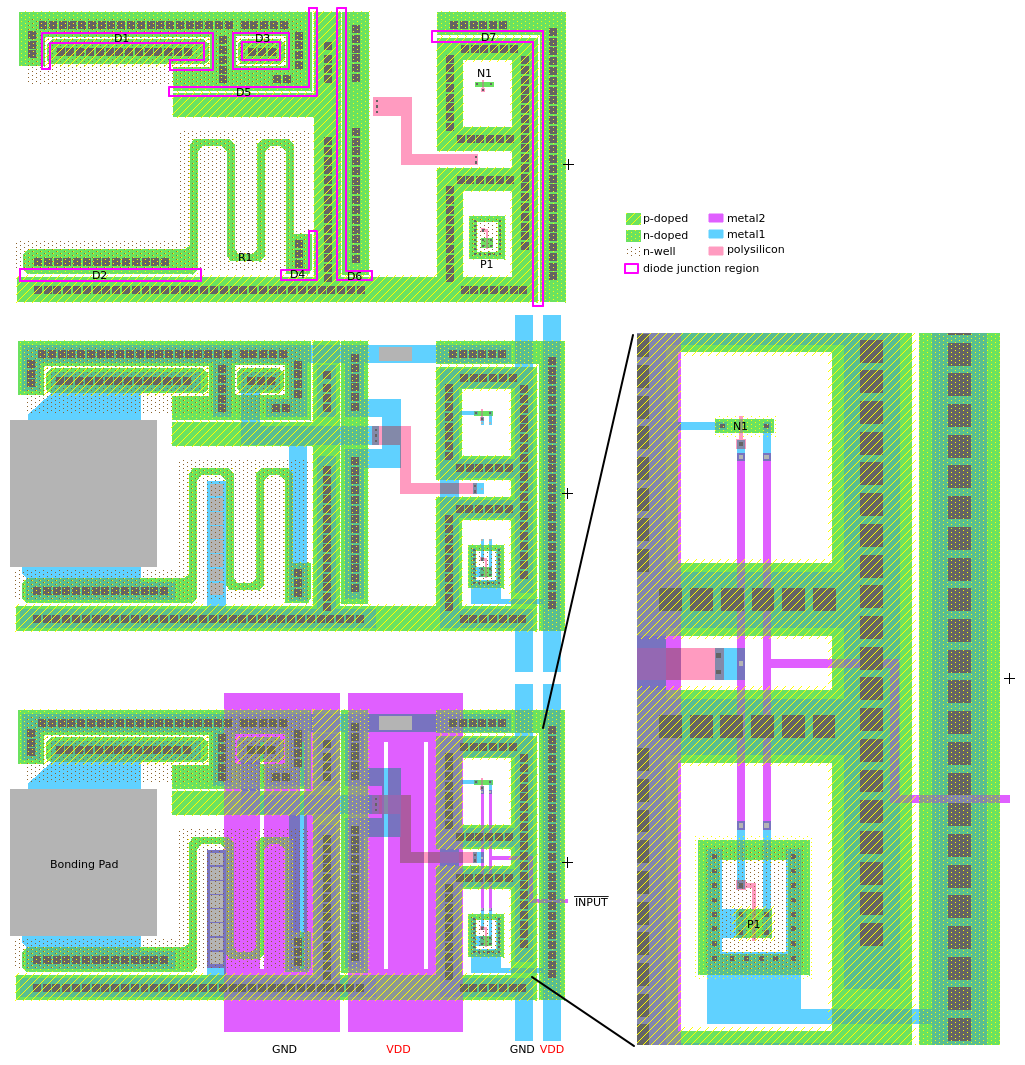

PAD_BIDIR (A)

Bidirectional pad with open-drain/-source capability.

This cell is found all around the edge of the chip and is rotated (not mirrored!) so that the three connections face inwards.

|

|

Instances: A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 MCS MRD MWR RD WR (21 total)

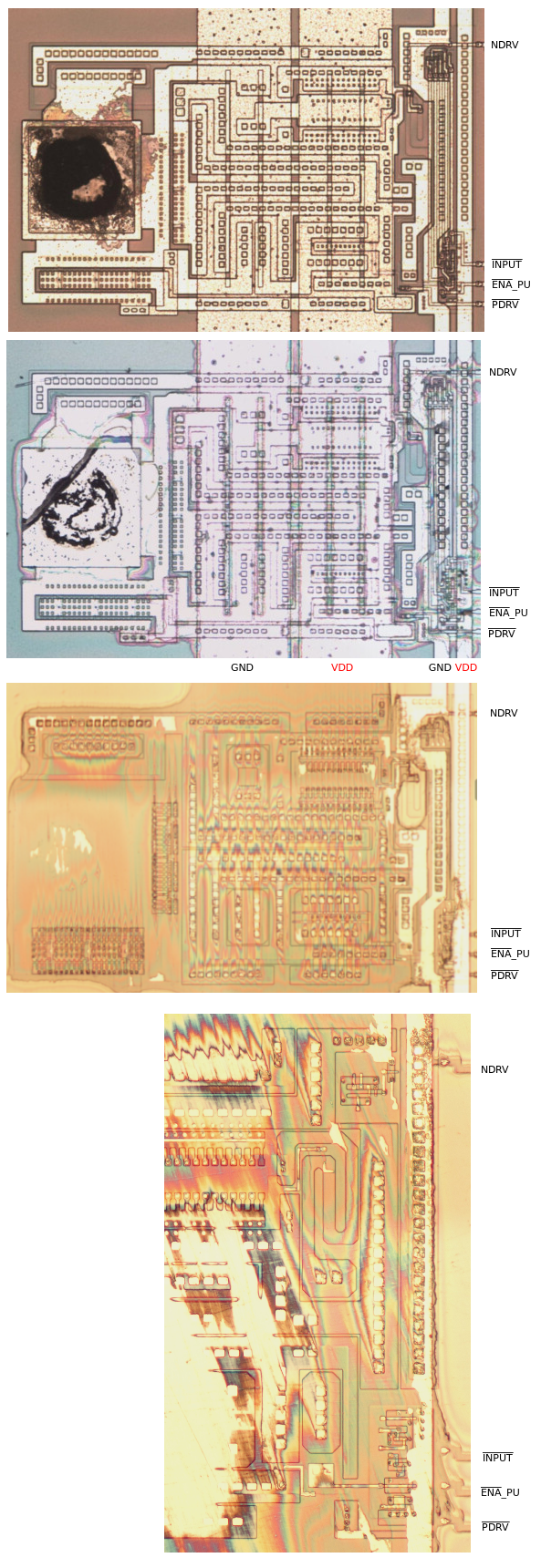

PAD_BIDIR_PU (B)

Bidirectional pad with open-drain/-source capability and optional pull-up resistor.

This cell is found all around the edge of the chip and is rotated (not mirrored!) so that the four connections face inwards.

|

|

Instances: D0 D1 D2 D3 D4 D5 D6 D7 MD0 MD1 MD2 MD3 MD4 MD5 MD6 MD7 P10 P11 P12 P13 SIN (21 total)

PAD_BIDIR_PU_LATCH (C)

Bidirectional pad with open-drain/-source capability, optional pull-up resistor, and input NAND latch.

This cell is only used for SCK. In the die shot this picture was taken from, this pin is located at the right-hand side. For consistency across this documentation it is rotated here (not mirrored!).

|

|

Instances: SCK (1 total)

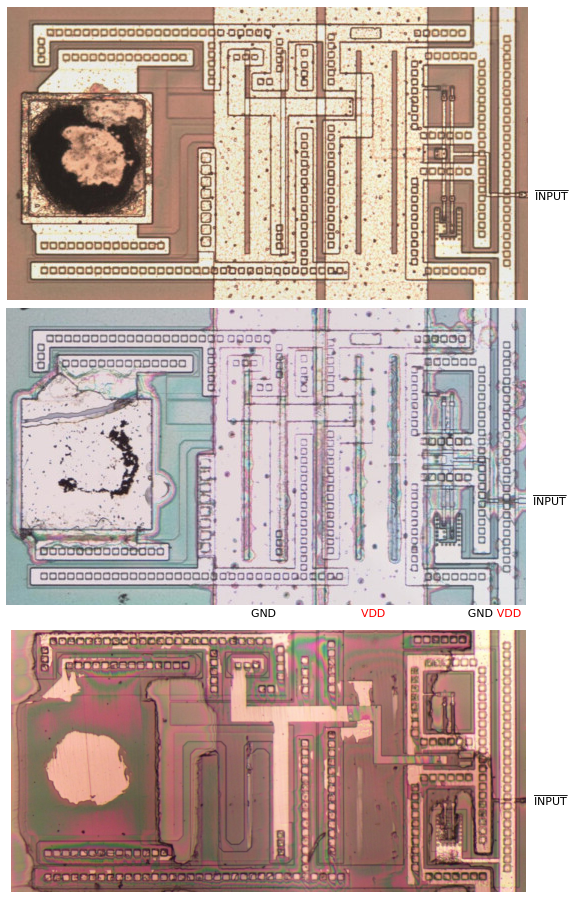

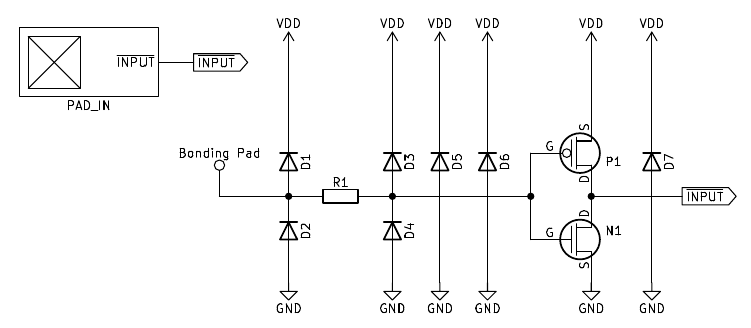

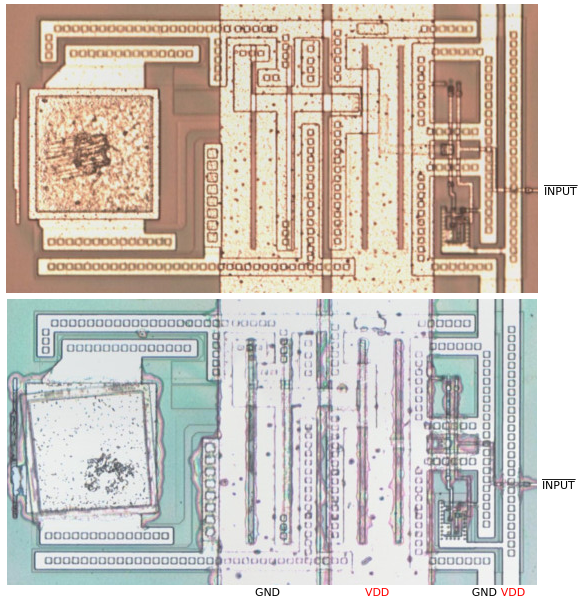

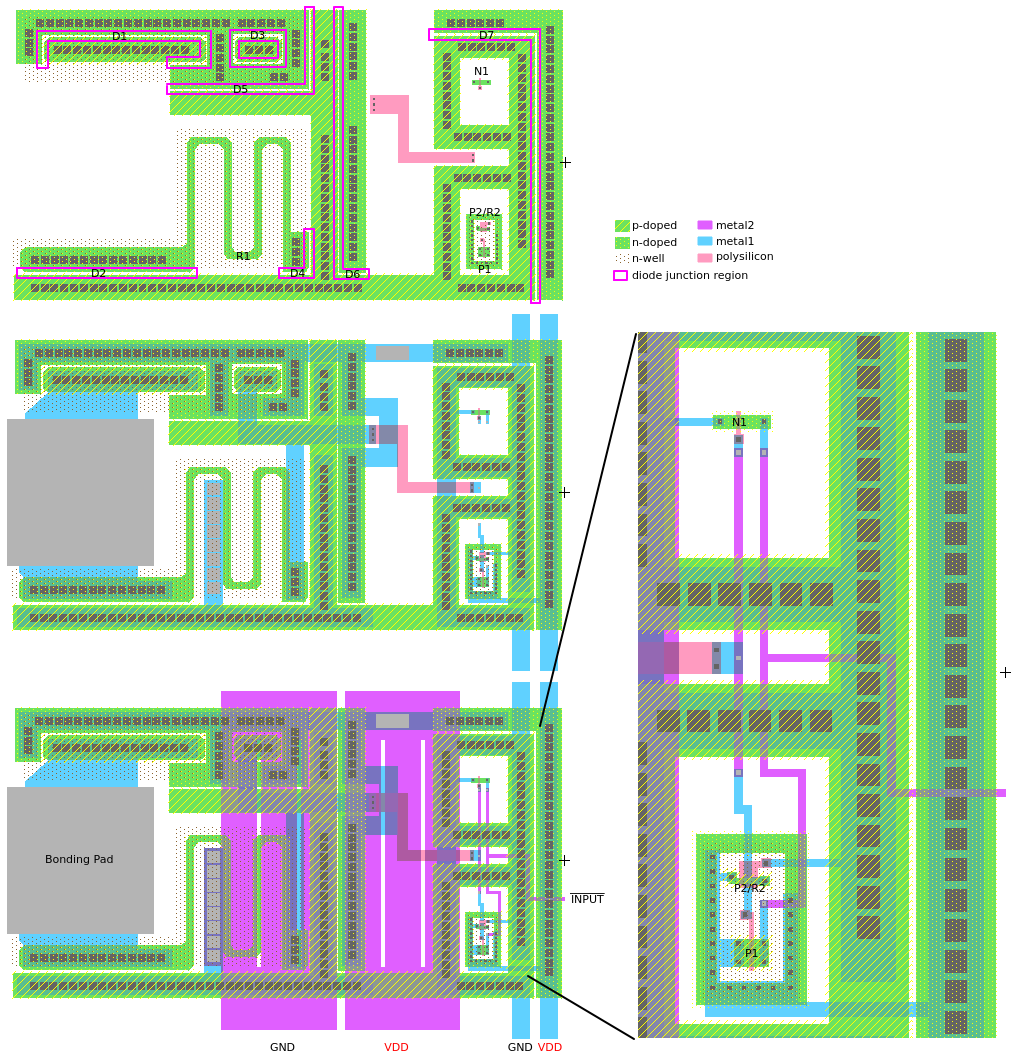

PAD_IN (A)

Simple inverting input pad.

This cell is only used for RESET, T1 and T2. In the die shot this picture was taken from, these pins are located at the right-hand side. For consistency across this documentation it is rotated here (not mirrored!).

|

|

Instances: RESET T1 T2 (3 total)

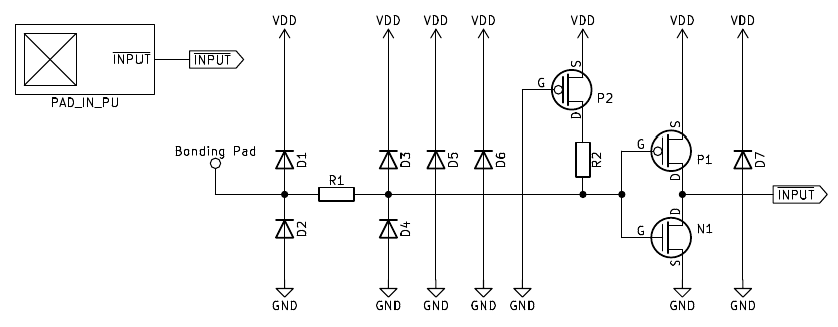

PAD_IN_PU (B)

Simple inverting input pad with pull-up resistor.

This cell is only used for the un-bonded NMI pad.

|

|

Instances: NMI (1 total)

PAD_OUT (A)

Simple inverting output pad.

This cell is found all around the edge of the chip and is rotated (not mirrored!) so that the connection faces inwards.

|

|

Instances: CP CPG CPL CS FR LD0 LD1 M1 MA0 MA1 MA2 MA3 MA4 MA5 MA6 MA7 MA8 MA9 MA10 MA11 MA12 PHI S SOUT ST (25 total)

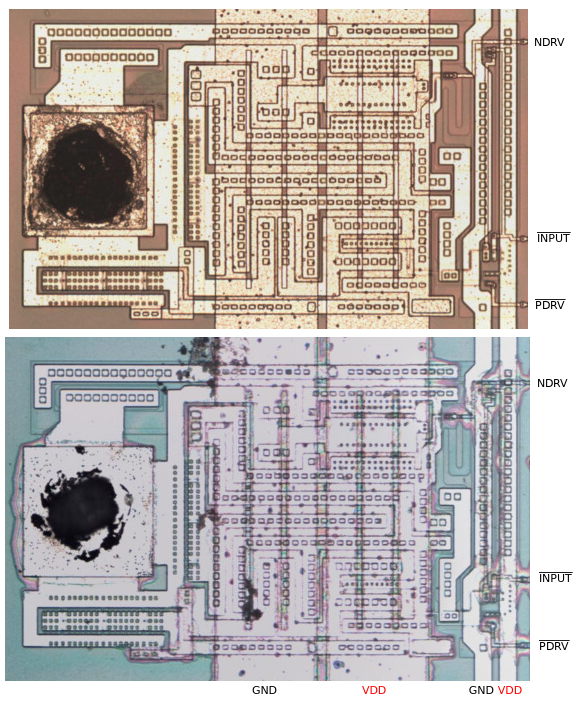

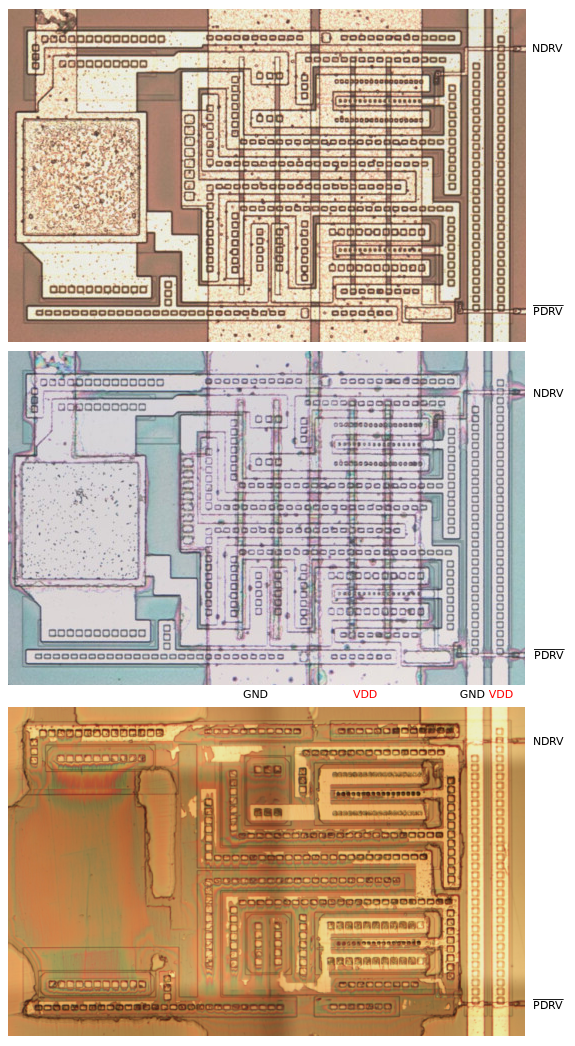

PAD_OUT_DIFF (B)

Output pad with open-drain/-source capability.

This cell is only used for P14 and P15. In the die shot this picture was taken from, these pins are located in the bottom right corner. For consistency across this documentation it is rotated here (not mirrored!). Keep that in mind, especially for P14, where the PDRV connection is at the top and NDRV is at the bottom.

|

|

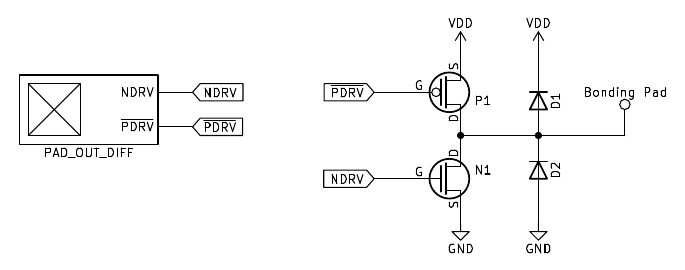

PAD_XTAL

Oscillator input and output pads for connecting external crystal.

This cell is only used for CK1/CK2. In the die shot this picture was taken from, these pins are located at the right-hand side. For consistency across this documentation it is rotated here (not mirrored!).

|

|

Instances: CK1/CK2 (1 total)

PAD_PASS

Simple pass pad with direct metal connection. Used as analog output.

This cell is only used for SO1 (ROUT) and SO2 (LOUT). In the die shot this picture was taken from, these pins are located at the bottom right. For consistency across this documentation it is rotated here (not mirrored!).

|

|

PAD_PASS_TG

Simple pass pad with transmission gate. Used as analog input.

This cell is only used for VIN. In the die shot this picture was taken from, this pin is located at the bottom right. For consistency across this documentation it is rotated here (not mirrored!).

|

|

Instances: VIN (1 total)

Analog

AMP

Audio amplifier.

|

|

The final stage of amplifiers that drive the SO1 (ROUT) and SO2 (LOUT) output pads have much bigger output transistors (P6 and N5), which are not contained within the amplifier cell. They are connected like this:

|

|

Instances: CH1_AMP, CH2_AMP, CH3_AMP, CH4_AMP, LADJ_AMP, RADJ_AMP, LOUT_AMP, ROUT_AMP (8 total)

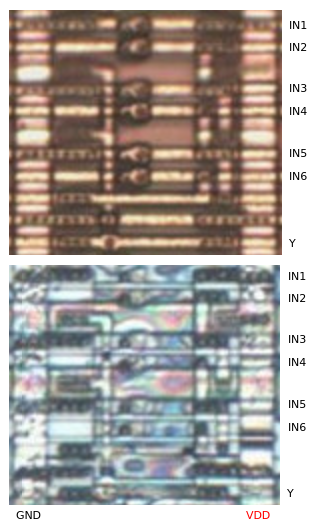

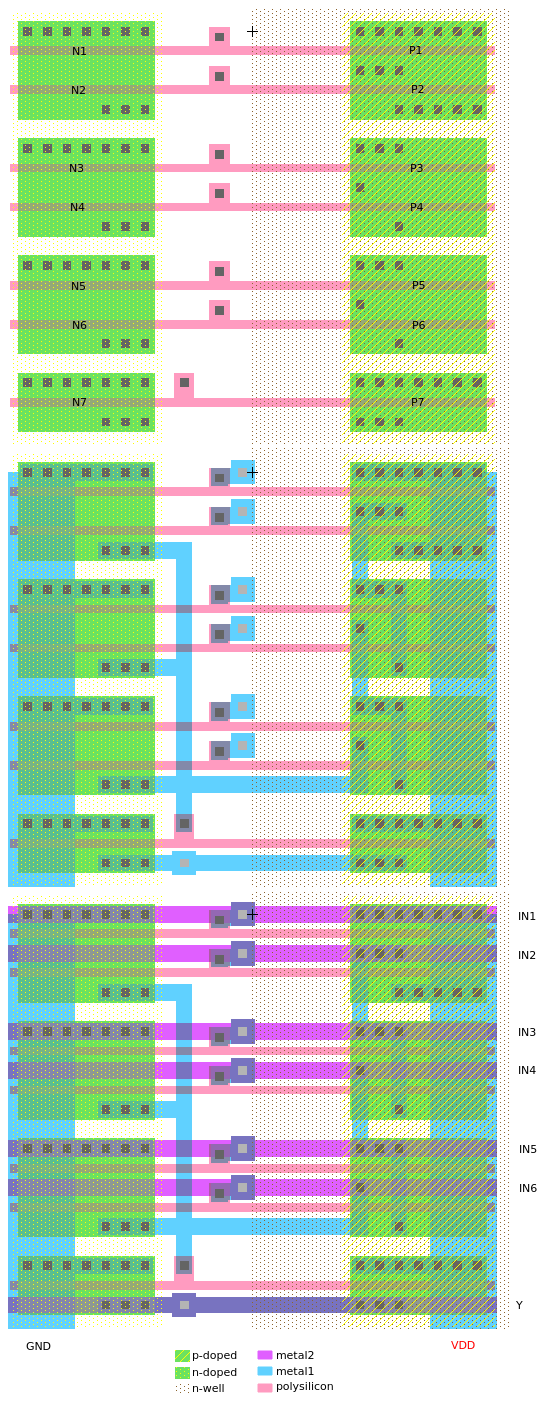

DAC

4-bit digital to analog converter.

|

|

Instances: CH1_DAC, CH2_DAC, CH3_DAC, CH4_DAC (4 total)

MIXER

5-channel analog mixer.

|

|

Instances: LMIX, RMIX (2 total)

RV

3-bit digital rheostat.

|

|

VDIV

Voltage divider.

|

|

Instances: VDIV (1 total)

Other

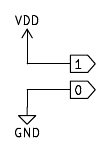

TIE

Constant supply.

The outputs of this cell are hardwired to VDD and GND. It is used to provide constant 1 and 0 signals to other cells. For example, it is used for the interrupt flags register: The PESU cell feeds a constant 1 into the data inputs of flip-flops (LOPE, UBUL, ...). Whenever the clock inputs of those flip-flops get triggered by an interrupt, the constant 1 gets clocked in.

Name in DMG-CPU-Inside: INVERTER? or BUFFER?

|

|

Instances: BOHY PESU RUNY VYPO WEFE (5 total)

GGNMOS

Grounded-Gate NMOS for ESD protection.

Instances: GGNMOS_SW, GGNMOS_NW, GGNMOS_NE, GGNMOS_SE (4 total)

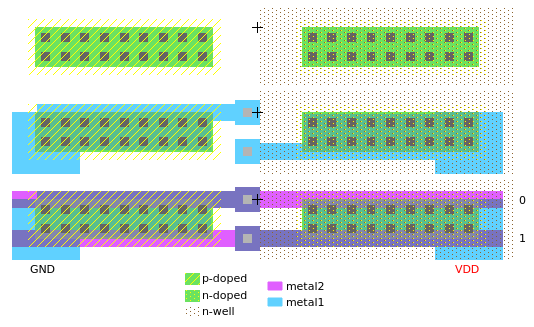

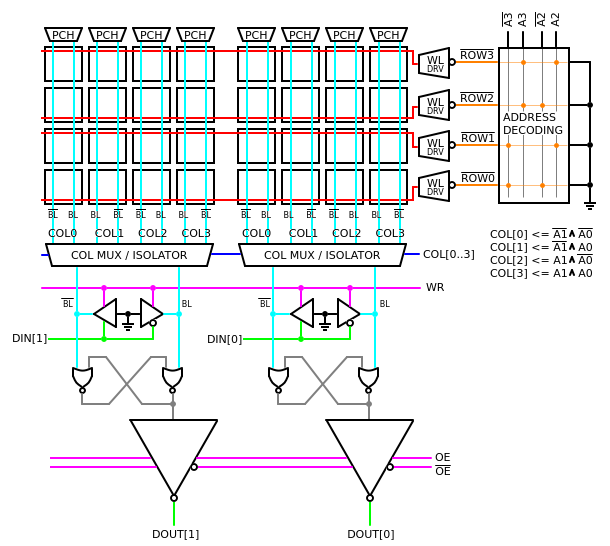

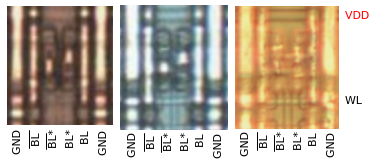

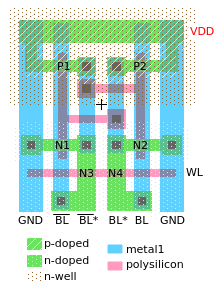

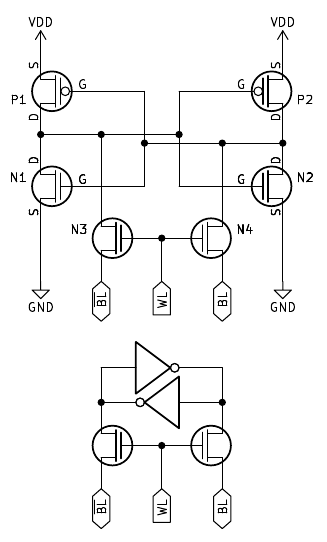

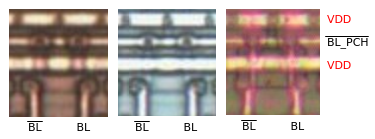

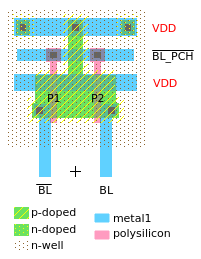

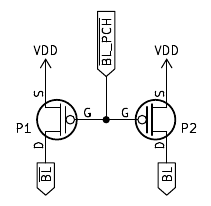

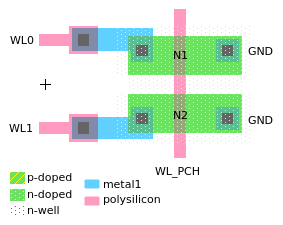

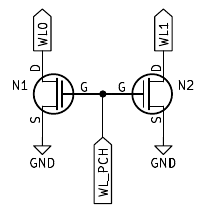

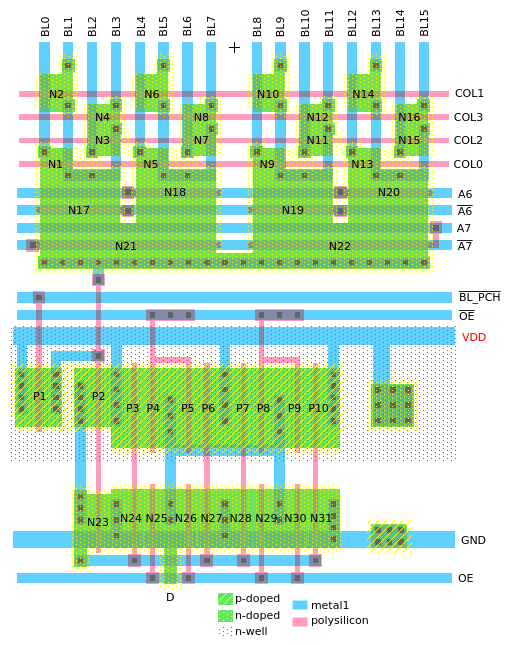

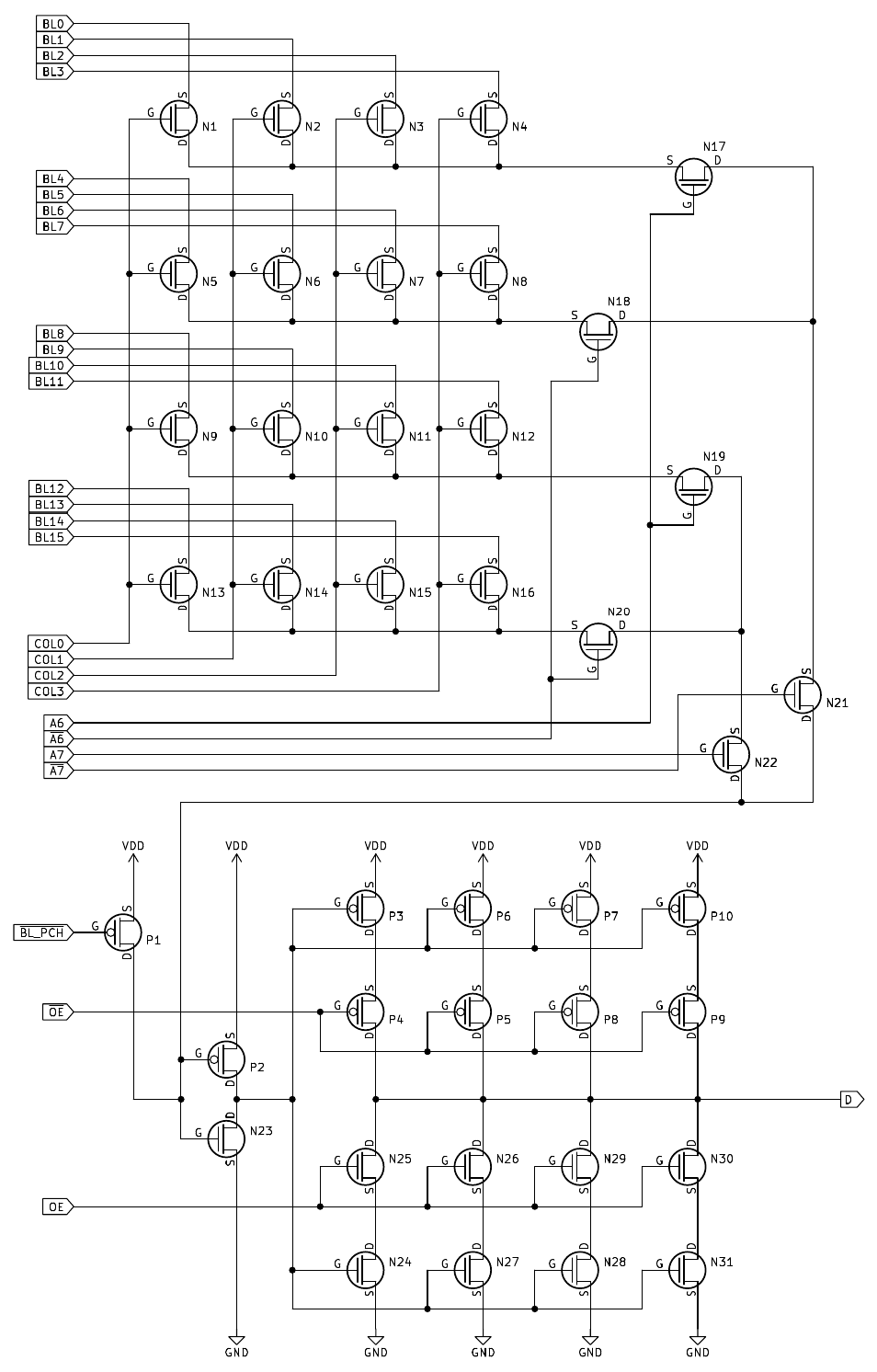

SRAM

Static RAM module with 6T bit cells.

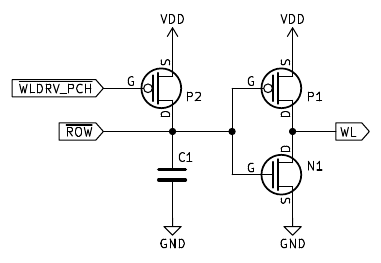

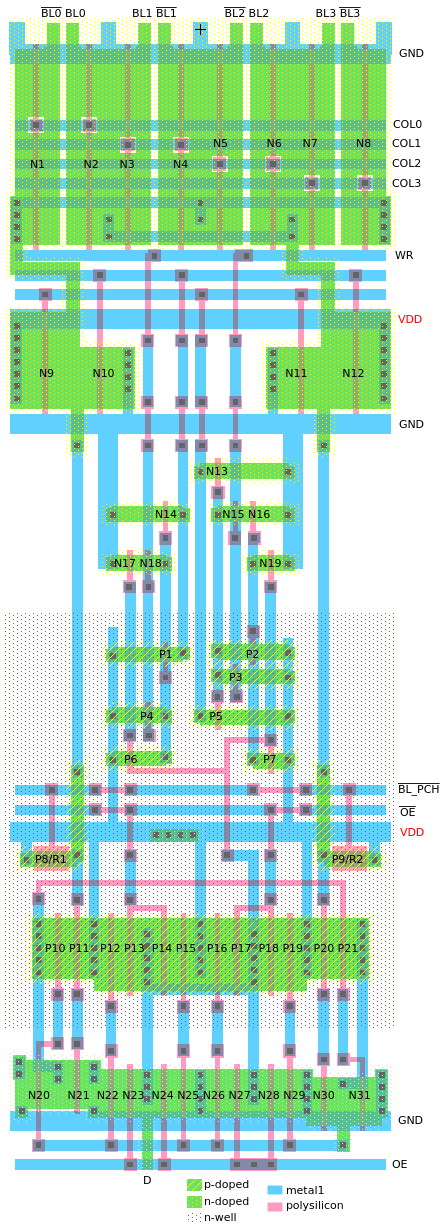

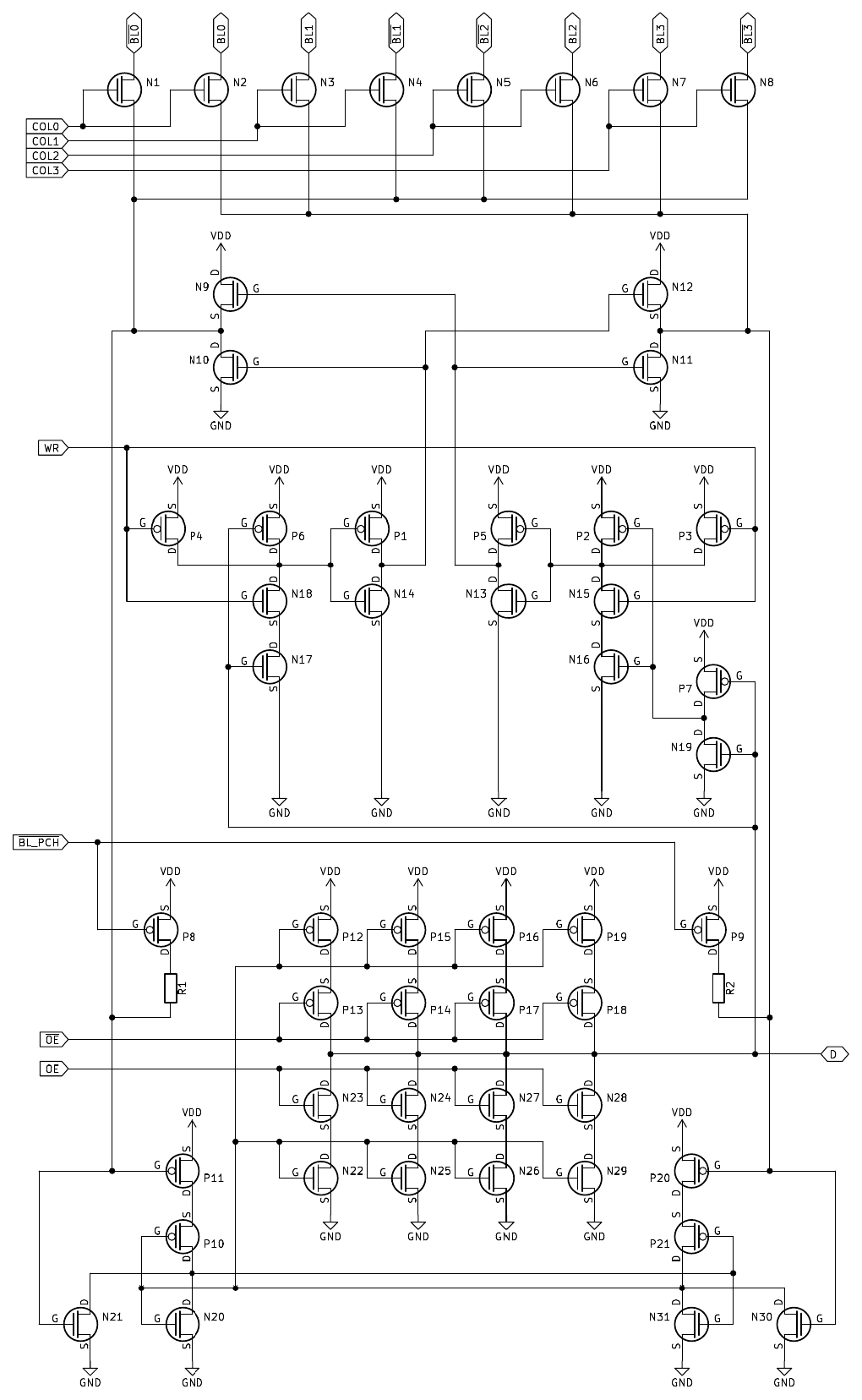

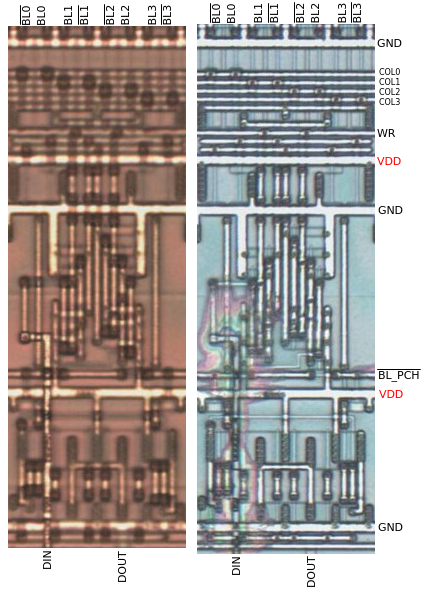

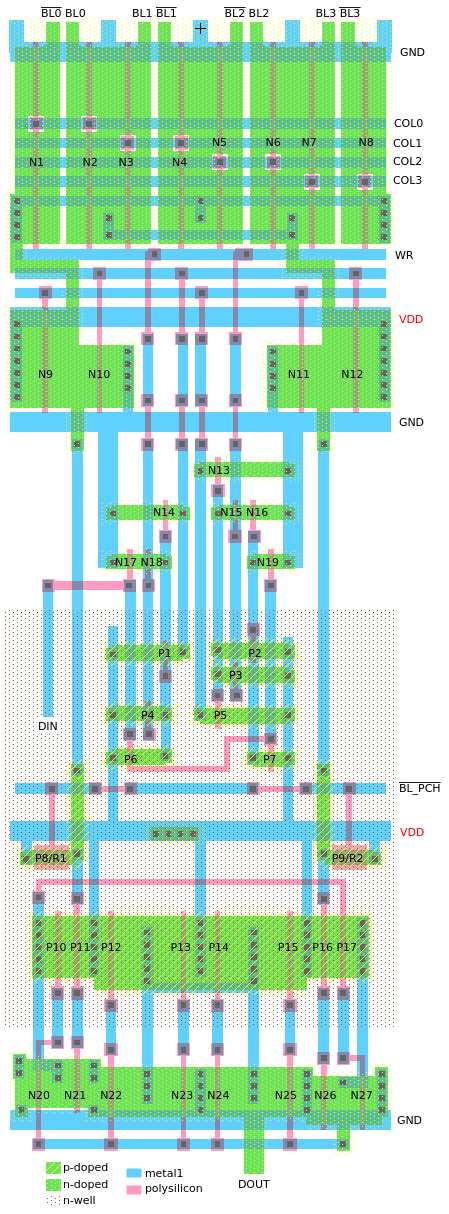

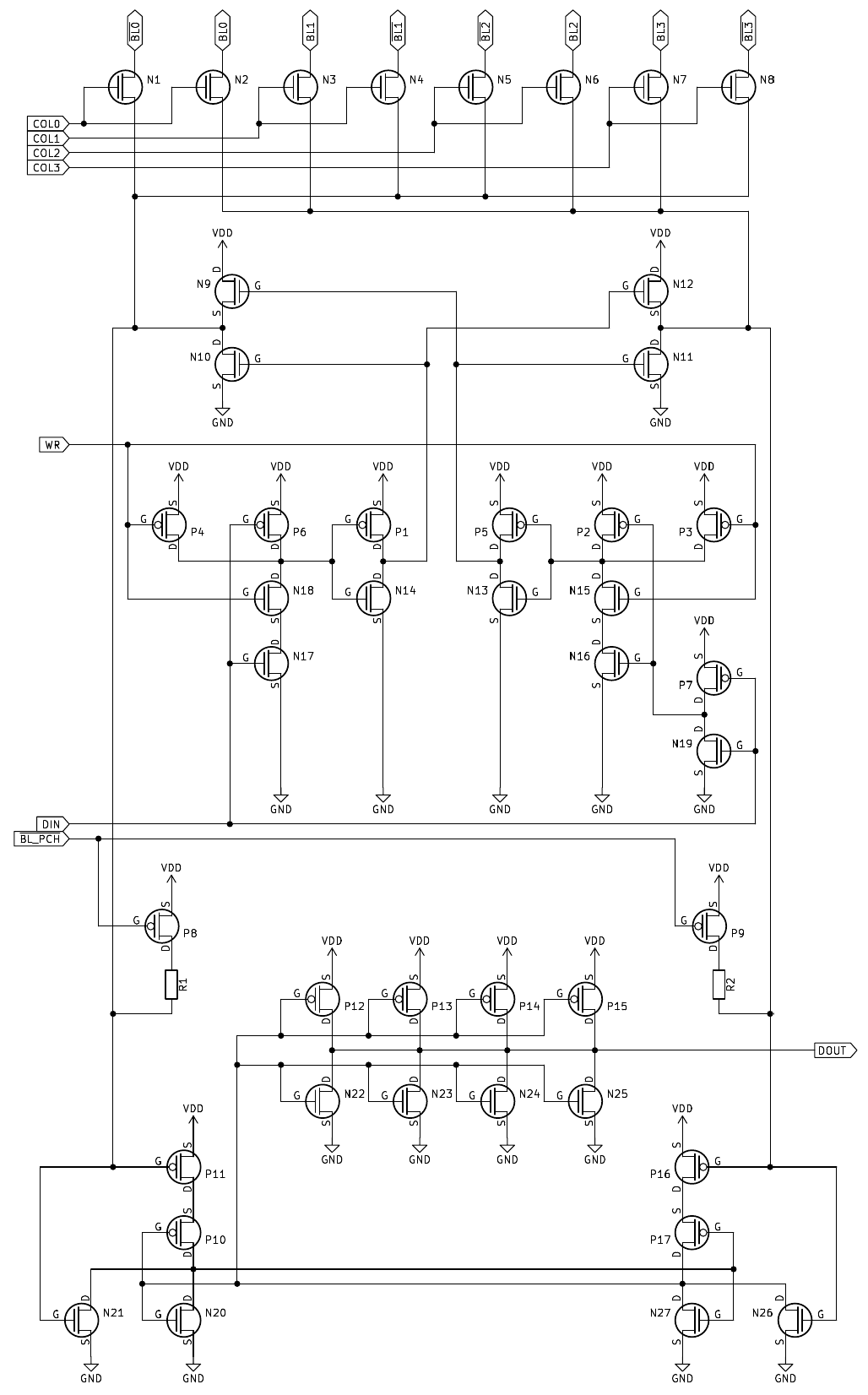

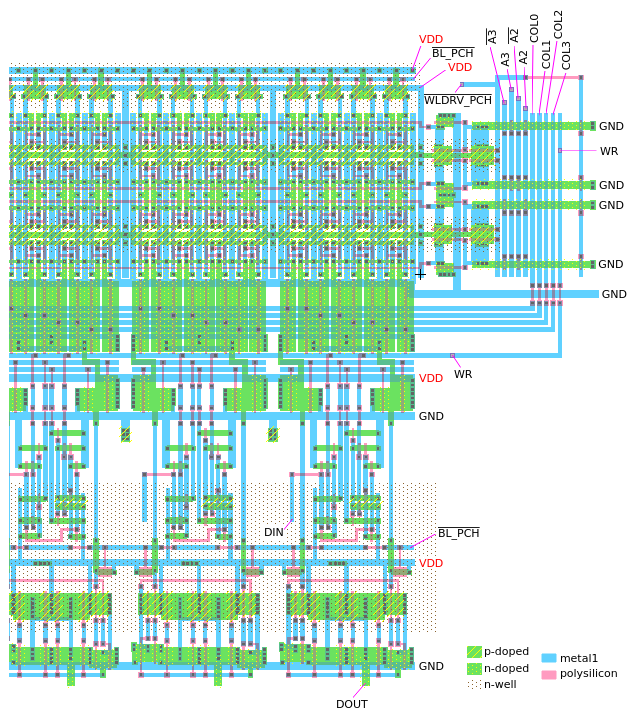

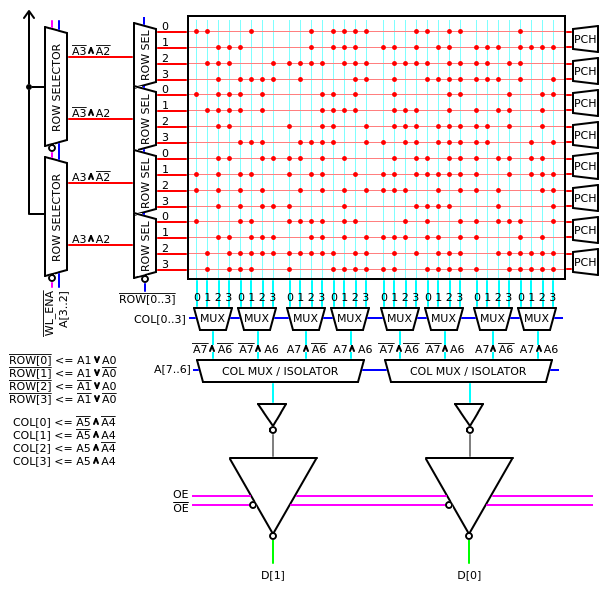

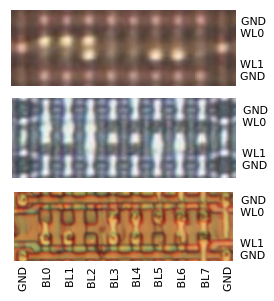

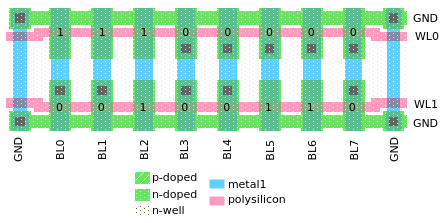

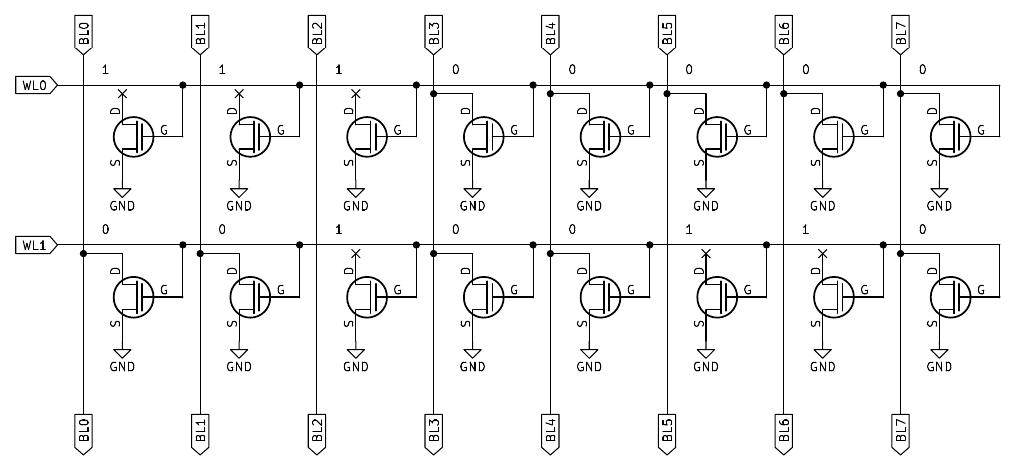

There are four instances of SRAMs on the DMG-CPU B chip: HRAM, Wave RAM and 2x OAM. The following picture shows the simplified structure of those SRAMs using the two least significant data lines of the Wave RAM as an example:

First of all, please note that the Wave RAM doesn't have output enable inputs (OE/OE). These are shown for completenes. The Wave RAM was selected as an example, because it is the smallest one. Also, the Wave RAM is the only one that has seperate data inputs and outputs (DIN/DOUT). The other SRAMs have bi-directional data I/Os, where DIN and DOUT are just wired together. That's why the other SRAMs have OE/OE and the Wave RAM doesn't. The Wave RAM its data outputs are always driving, even when writing or during bit line precharging.

Each bit consists of six transistors: Two PMOS and two NMOS forming two CMOS inverters that are feeding each other, plus two more NMOS transistors that are controlled by the word line (WL), connecting both sides of the inverter pair to the bit lines (BL/BL). Since there are no PMOS transistors complementing those two NMOS, the connection between inverters and bit lines can only pass "zeroes" through efficiently. To guarantee the bit lines are in a defined state, they need to be precharged (PCH) with "ones" before each memory access. This means reading and writing the bits is implemented in dynamic NMOS logic. Writing a bit requires a "strong" zero being put on one of the bit lines, overpowering the inverters and making them flip.

Address decoding on the right hand side is also implemented in dynamic NMOS logic. So, the word line drivers require precharging before each memory access too. Address lines A2 and upwards are fed into the address decoder, selecting one word line or row. A0 and A1 are used to select one of the four columns. The column muxer consists of very huge NMOS transistors, so again, only zeroes can really pass through.

Bit description:

|

|

Bit line precharger description:

|

|

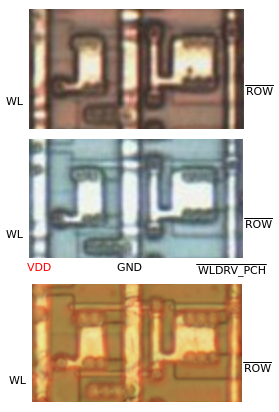

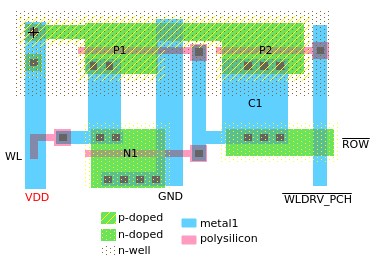

Word line driver description:

|

|

Sense amplifier, write logic and column muxer description - Variant A (used in HRAM and OAM):

|

|

Sense amplifier, write logic and column muxer description - Variant B (used in Wave RAM):

|

|

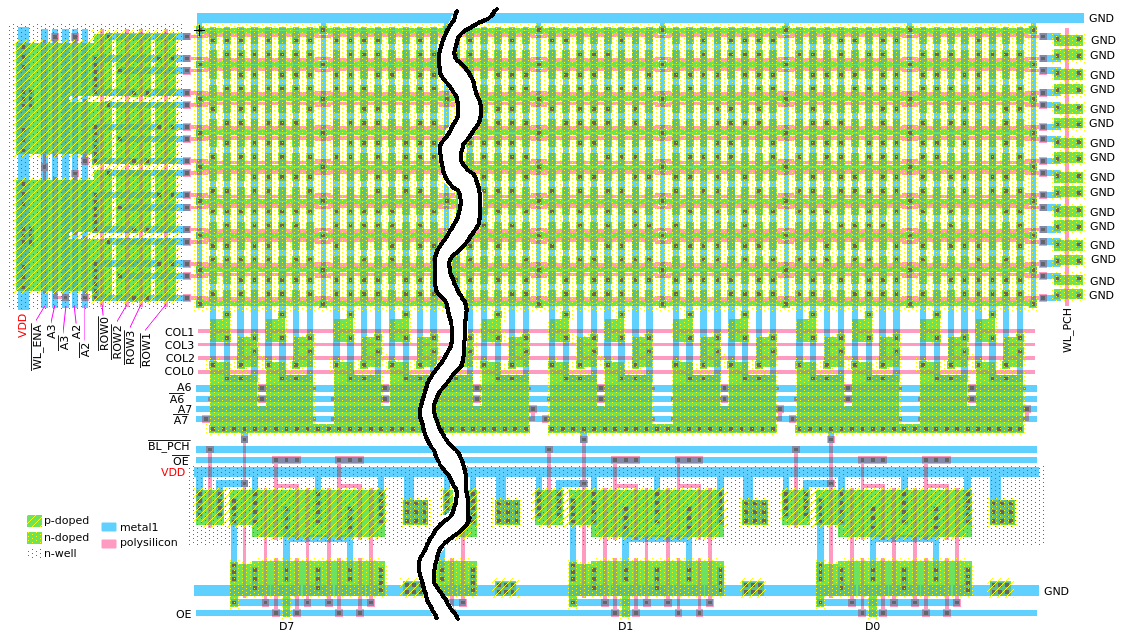

WAVE_RAM

16 byte SRAM, organized in four rows and four columns for each of the eight bits.

Position of all the I/Os of the Wave RAM:

For detailed information, see the SRAM section above.

Instances: WAVE_RAM (1 total)

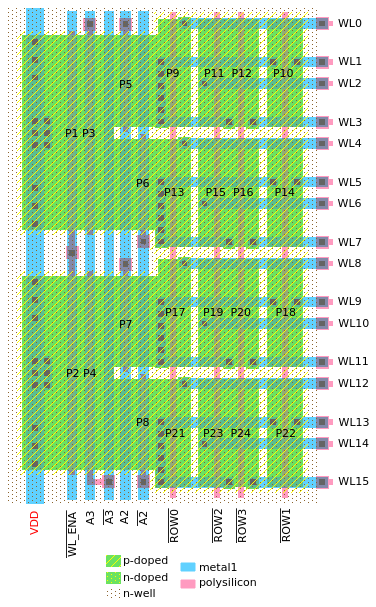

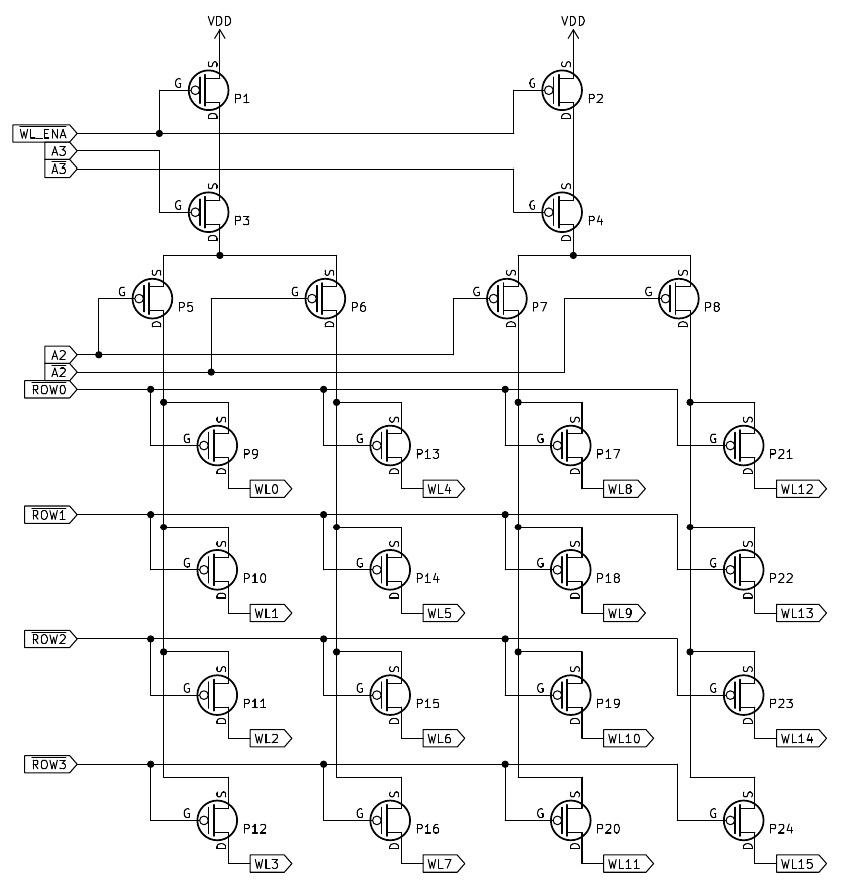

ROM

Masked ROM module.

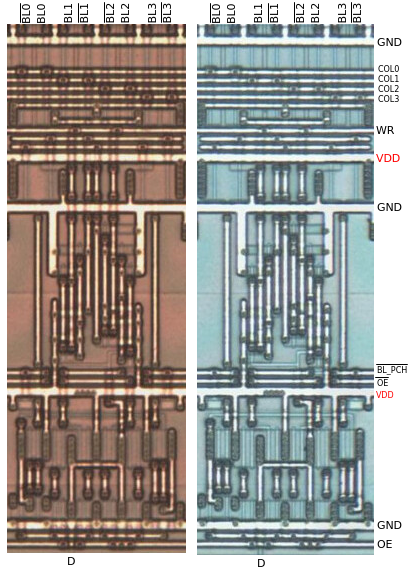

There is only one ROM instance on the DMG-CPU B chip: The boot ROM. The following picture shows the simplified structure of the boot ROM. Only the two least significant bits are drawn:

Each bit is represented by a single NMOS transistor. Only the transistors that are representing "zero" bits are actually connected to the respective bit line (column). "One" bits have a dummy transistor that has no connection to its drain. The sources of all transistors are connected to ground and the gates are connected to their respective word lines (rows).

Bits description (picked random 16 bits from the boot ROM as example):

|

|

Row selector description:

|

|

Word line precharger description:

|

|

Sense amplifier and column muxer description:

|

|

BOOT_ROM

256 byte masked ROM, organized in 16 rows and 16 columns for each of the eight bits.

Position of all the I/Os of the Boot ROM:

For detailed information, see the ROM section above.

Instances: BOOT_ROM (1 total)